RISC-V

RISC-V (prononcé en anglais « RISC five » et signifiant « RISC cinq ») est une architecture de jeu d'instructions (instruction set architecture ou ISA) RISC ouverte et libre, disponible en versions 32, 64 et 128 bits. Ses spécifications sont ouvertes et peuvent être utilisées librement par l'enseignement, la recherche et l'industrie.

RISC-V est implémenté dans différents SoC, à destination de l'embarqué, des objets connectés (supportés par différentes systèmes temps réels ou à destination de l'embarqué, tels que Arduino, FreeRTOS, HarmonyOS, LiteOS, RT-Thread, RustOS, Zephyr…), d'ordinateurs légers sous formes de SBC, généralement avec Linux (Debian, Fedora, Ubuntu) ou encore des variantes d'OpenWrt, de serveurs, et un projet européen initié en 2019, vise à l'utiliser dans des supercalculateurs domestiques comme accélérateurs au sein de SoC basse consommation développés localement et fonctionnant sous GNU/Linux, comme la grande majorité des supercalculateurs.

Motivations

Ce projet, créé initialement au sein de la division informatique de l'Université de Californie à Berkeley, aux États-Unis, avait d'abord une visée d'étude et de recherche, mais est devenu de facto un standard d'architecture ouverte dans l'industrie.

Le but de ce projet est de faire un standard ouvert de jeu d'instructions de microprocesseur, à l'image du standard TCP/IP pour les réseaux ou d'UNIX pour les systèmes d'exploitations, l'architecture des processeurs étant pour le moment toujours fermée, restreignant les progrès, les implémentations ou le support dans les systèmes d'exploitation[1].

Historique

La conception du processeur commence en 2010 à l'université de Californie Berkeley, dans le but de développer un processeur avec les connaissances du XXIe siècle, n'ayant pas à traîner le fardeau de la compatibilité avec des architectures vieilles de 20 ans, comme ARM ou l'architecture x86 d'Intel et en voulant par la même occasion que l'architecture de jeu d'instructions du processeur (ISA) reste ouverte[2].

En 2014, la version 2.0 des spécifications est publiée, plusieurs industriels importants sont intéressés par le projet [2].

En 2015, la fondation RISC-V est créée avec plus de 100 membres, avec un directoire composé d'entreprises comme Google, Nvidia, Western Digital, NXP Semiconductors, Microsemi, et Bluespec, ainsi que des représentants de l'Université de Berkeley. Depuis, des compagnies telles que AMD, Qualcomm, et IBM l'on rejoint[2].

En 2016, Nvidia prévoit d'utiliser un microcontrôleur RISC-V pour ses GPU et pense ainsi multiplier par 3 ses performances par rapport à son propre microcontrôleur, Falcon[3],[2]. Le Falcon est également un processeur d'architecture RISC, mais avec adressage limité à 32 bits et pas de protection de threads et avec ses limitations. Nvidia désire donc le remplacer par la version 64 bits de RISC-V, bénéficiant ainsi d'un adressage 64 bits, des corrections d'erreur, d'un jeu d'instructions extensible et d'une amélioration de la sécurité[4].

En 2017, la version 2.2 des spécifications est publiée. Mozilla annonce que son langage Rust peut être compilé vers l'architecture RISC-V. Le fabricant de disques durs Western Digital annonce qu'il va livrer des milliards de ses équipements équipés d'un contrôleur d'architecture RISC-V[2].

Le , une partie de la direction de la société ARM décide de faire un site nommé « riscv-basics.com » contre RISC-V, sentant son marché menacé, notamment parce qu'une partie importante de ses plus gros clients (voir plus haut) commence également à développer des solutions basés sur RISC-V. Cette action met en colère le personnel technique de la société qui y voit une attaque contre le mouvement open-source. Cela a également pour effet de faire connaître un peu plus RISC-V et de faire davantage comprendre qu'il s'agissait d'une alternative viable. La direction d'ARM décide finalement de fermer le site dès le lendemain, le 2018[5],[6].

En 2019, le gouvernement américain de Donald Trump met la pression sur les fondeurs de micro-électronique, tels que le taïwanais TSMC, le plus important au monde, pour qu'ils déménagent leur activités sur le sol américain, ce que ce dernier refuse[7], tout en menaçant ceux qui continueraient de travailler avec les entreprises chinoises telles que Huawei[8]. À la suite des risques politiques de ces pressions, la Fondation décide de s'implanter dans un pays neutre : la Suisse[9],[8],[3].

En , Nvidia cherche des spécialistes RISC-V pour l'intégrer comme processeur au sein de ses SoC Tegra[3].

En , Huawei sort ses nouveaux microcontrôleurs maison à base de RISC-V, ainsi que les kits de développement matériel et logiciel correspondants[10].

En , Haiku est porté sur RISC-V ; gel des fonctionnalités de Debian Bulleseye en vue de la sortie de la première version de la distribution à supporter officiellement RISC-V. Le pilote graphique Radeon HD pour Linux est porté sur l'architecture[11].

Spécifications

Elle implémente un jeu d'instruction RISC, sans microcode, ni surcouche d'architecture du type exécution dans le désordre ou dans l'ordre, ou bien le support d'un type de matériel en particulier (ASIC, FPGA…), mais ceux-ci peuvent être implémentés avec toutes leurs fonctions.

- révision de 2008 du standard IEEE-754 pour l'unité de calcul de nombres en virgule flottante.

- Adressage 32, 64 ou 128 bits.

- Possibilité pour chaque implémentation d'apporter des instructions étendues.

- Support d'implémentation multicœurs hautement parallèles et d'architecture multiprocesseurs hétérogènes.

- Instructions de longueur variable en option, permettant à la fois d'augmenter l'espace d'encodage des instructions disponibles, mais également de rendre les instructions plus denses afin d'améliorer les performances, de réduire la taille du code statique et l’efficacité énergétique.

- Une architecture complètement virtualisable pour faciliter le développement d'hyperviseur.

Des chercheurs de l'Université de Californie à Berkeley, ont également développé une version appelée BOOM, ajoutant une gestion d'exécution dans le désordre des instructions, dans le modèle RV64G[12].

Nomenclature des extensions

Le nom du processeur a une signification :

- La base est constituée de RV (pour RISC-V), puis de 32, 64 ou 128, selon le nombre de bits, et enfin, d'un I ou d'un E (embedded, c'est-à-dire embarqué)[13].

Les noms de bases possibles sont donc :

- RV32I

- RV32E (embarqué)

- RV64I

- RV128I

Le nom du processeur est suivi d'une ou plusieurs lettres décrivant les extensions qui sont ajoutées à la base[13] :

- M – Extension standard de multiplications et divisions entières ;

- A – Extension standard d'instructions atomiques ;

- F – Extension standard de virgule flottante simple précision (32 bits) ;

- D – Extension standard de virgule flottante double précision (64 bits) ;

- G – Général, raccourci pour les instructions de base, et les jeux d'instructions ci-dessus, c'est-à-dire, M,A,F,D)

- Q – Extension standard de virgule flottante quadruple précision (128 bits) ;

- L – Extension standard de virgule flottante, décimal ;

- C – Extension standard d'instructions compressées ;

- B – Extension standard de manipulations de bits ;

- J – Extension standard de langages traduits dynamiquement (Compilation à la volée, Just in time ou JIT), cela concerne les langages de scripts tels que C#, Haskell, Java, JavaScript, Lua, OCaml, PHP, Python, R, Ruby, Scala, WebAssembly, etc ;

- T – Extension standard de mémoire transactionnelle ;

- P – Extension standard d'instructions SIMD compactées (Packed SIMD) ;

- V – Extension standard d'opérations vectorielles ;

- N – Extension standard d'interruptions utilisateur ;

- S – Extension standard de Superviseur ;

- H – Extension standard d'Hyperviseur, similaires à S mais commençant par un S[14].

ISA 32 bits de base

Le jeu d'instructions de base est composé de 47 instructions, dont huit instructions systèmes (appels systèmes, compteurs d'exécution), le reste étant réparties dans les catégories calcul, contrôle de flux et accès mémoire[15].

la version RV32I comporte 32 registres généraux 32 bits, tandis que la version RV32E (embarqué, embedded) ne comporte que 16 registres généraux 32 bits. Les deux comportent en plus un registre PC[16].

Instructions de calcul

Toutes les instructions de calcul utilisent trois opérandes, sauf lui et auipc qui n'en ont que deux (un registre destination et une valeur immédiate). Le premier opérande est le registre de destination, le second le registre source et le troisième, soit un second registre, soit une valeur immédiate (précisé par un i dans le mnémonique de l'instruction, sauf auipc ayant un autre sens)[15] (Les instructions de multiplication et division entières sont contenus dans l'extension M) :

add,addi,sub: addition et soustraction addi est utilisé avec une valeur immédiate négative pour la soustraction d'une valeur immédiate.sll,slli,srl,srli,sra,srai: décalage bit à bit (shift) + gauche/droite (en), logique (logical) ou arithmétique (arithmetic).and,andi,or,ori,xor,xori: opérations logiques bit à bit comprenant et (and), ou (or) et ou exclusif (xor).slt,slti,sltu,sltui, (set if less than) met le registre de destination à 1 si le premier opérande source est égal ou inférieur au second. Le u signifiant non-signé (unsigned). Les opérandes immédiats sont limités à 12 bits.lui, charge la partie immédiate de poids fort (load upper immediate), i.e. les bits 12 à 31 du registre de destination avec une valeur immédiate sur 20 bits. Il faut utiliseraddiavec une valeur immédiate de 12 bits, pour compléter la valeur.auipcajoute la valeur immédiate au 20 bits de poids forts du compteur ordinal (PC), il faut également utiliséaddipour les 12 bits de poids faible

Contrôle de flux

Instruction de branchement conditionnels[15] :

beq,bne,blt,bltu,bge,bgeu, instruction de branchement (branch) conditionnel à deux opérateurs, égal (equal), différent (not equal), plus petit (littler than), plus grand ou égal (greater or equal), signé (par défaut) ou non (unsigned).

Branchements inconditionnels[15] :

jal(jump and link), passe le contrôle à l'adresse du PC à laquelle est ajoutée la valeur immédiate 20 bits signée fournie. Ajoute l'adresse de l'instruction suivante (adresse de retour à la fin de la fonction appelée) dans le registre de destination.jalr(jump and link, register), l'adresse du saut est calculée par l'addition du registre source et de la valeur immédiate sur 12 bits, et l'adresse de l'instruction est chargée dans le registre de destination. Si cette instruction est précédée d'une commande auipc, le saut peut être effectué dans l’entièreté de l'espace mémoire 32 bits.

Accès mémoire

Les instructions d'accès mémoire servent à transférer des données entre un registre et la mémoire. Le premier opérande est le registre, le second un registre contenant l'adresse, le troisième une valeur immédiate sur 12 bits signée ajoutée au contenu du registre utilisé pour l'adressage, afin de déterminer l'adresse finale[15] :

lb,lbu,lh,lhu,lw, chargement (load) d'un octet (byte), demi-mot (half-word, 16 bits), ou mot (word, 32 bits) de la mémoire vers un registre de destination. Les instructions sont étendues par le signe (défaut) ou par des zéros (unsigned).sb,sh,sw, stockage (store), un octet (byte), demi-mot (half-word, 16 bits), ou mot (word, 32 bits) vers la mémoire.fence, force l'ordonnancement de l'accès à la mémoire dans un contexte multithread, en assurant notamment la cohérence des caches.fence.i, permet de s'assurer que les opérations depuis stockage vers les mémoires d'instructions (par exemple cache instruction) soient terminées avant leur exécution. Elle est principalement utilisée dans le cas de code automodifié.

Instructions système

Une instruction sert à invoquer un appel système et un autre initialise un point d'arrêt pour le débogueur[15] :

ecall, appel systèmebreak, ajout d'un point d'arrêt.

Six instructions servent à lire et écrire dans les registres de contrôle et statut du système (control and status registers CSR). Le registre CSR est lu dans un registre général, puis mis à jour de façon atomique[15] :

csrrw,csrrwi,csrrc,csrrci,csrrs,csrrsi,

Les 6 registres CSR 32 bits suivants (correspondant à 3 valeurs 64 bits, de compteurs d’exécution) sont définis en lecture seule [15] :

cycle,cycleh, compteur de cycles d'horloges passés depuis un temps de référence. Ce temps peut varier si le mode de changement de fréquence ou de tension dynamique (dynamic voltage and frequency scaling (DVFS)) est actif ;time,timeh, compteur de temps-réel passé depuis un temps de référence (typiquement, démarrage du système) ;instret,instreth, compteur d'instructions processeur exécutées (instruction retired).

ISA 64 bits de base

L'ISA 64 bits étend les registres et l'espace l'adressage de 32 bits à 64 bits (XLEN=64). Les instructions comportant le suffixe W (anglais : Word, signifiant mot), indique que leur action est limité à un mot (32 bits) et ne se préoccupe pas des 32 bits supérieurs des entrées. Le bit de signature est déplacé vers le 64e bit (bit 63) des registres, il est donc important d'utiliser les fonctions spécialisées lors d'utilisation de données 32 bits[17].

Cela à aussi des implications sur les opérations immédiates. Par exemple, l'opération d'addition immédiate addi utilisant une valeur immédiate de 12 bits, addiw ignore les dépassements des 32 bits, et place de le bit de signe sur le bit 63 des registres[17].

Extension vectorielle

L'extension vectorielle comporte trois variables, ELEN (nombre de bits d'un élément), VLEN (nombre de bits d'un vecteur) et SLEN (distance de (stripping) entre deux éléments) qui doivent tous trois être une puissance de 2[18].

Elle comporte 32 registres de vecteurs nommés de v0 à v31, qu'il est possible de grouper par deux, dans ce qui est appelé groupe de registre de vecteur (vector register group) pour améliorer la précision ou bien améliorer les performances. Il y a également six registres de contrôle et statut (en) (CSR) (vstart, vxsat, vxrm, vtype, vl, vlenb) [18].

GPU RV64X

Un groupe de travail propose en une extension GPU appelée RV64X basée notamment sur l'extension de processeur vectoriel et le format VBlock proposé par le projet Libre GPU pouvant être implémenté en ASIC ou FPGA. La première version a pour objectif d'utiliser un pilote compatible avec l'API Vulkan de Khronos, pour plus tard supporter OpenGL et Direct3D. Il devrait également s'adresser dans un premier temps au domaine de l'embarqué. Les contraintes fixées sont[19] :

- Instruction 64 bits ;

- Support des fonctions complexes sin, cos, atan, pow, exp, log, rcp, rsq, sqrt, etc.

- Des vecteurs supportant 2 à 4 éléments en 8, 16 ou 32 bits ;

- Des matrices carrées 2 × 2, 3 × 3 et 4 × 4 ;

- pixels aux formats 8, 16, 32 et 64 bits ;

- Les points en 4 dimensions XYZW, 64 ou 128 bits ;

- Les pixels en 4 composantes RVBA, avec 8, 16, 24 ou 32 bits par composante ;

- Les texels ont 3 composantes UVW, en 8 ou 16 bits ;

- Support de variables de lumière, Ia, ka, Id, kd, Is, ks…

NEOX

En , la société Think Sillicon proposé un GPU basé sur l'architecture RISC-V[20].

Autre GPU basé sur RISC-V, avorté

En 2018, le projet Kazan ou Libre RISC-V avait pour objectif de développer un GPU basé sur RISC-V. En 2020, en raison de différents désaccords avec le fonctionnement de la fondation RISC-V, les auteurs du projet se réorientent vers une architecture OpenPower, version ouverte de Power, l'architecture RISC des années 1990 d'IBM[21], Les auteurs se tournent finalement sur la création d'une extension de processeur vectoriel appelée SV pour l'architecture Power, proche de l'extension V de RISC-V, plutôt que le développement d'un GPU.

Support logiciel

Une série d'outils libres est proposée pour le développement sur cette architecture, incluant la compatibilité des compilateurs GCC et LLVM (donc Clang), le support du débogueur GDB, ainsi que de l'hyperviseur et émulateur QEMU[22]. Le langage Rust supporte RISC-V depuis [23],[24].

Au niveau assembleur, GNU Assembler support les architectures RISC-V 32 et 64 bits (assembleur, désassembleur), et riscv-assembler est un assembleur en Python.

BronzeBeard[25] est un assembleur RV32IMAC écrit en Python liant le programme assemblé à une bibliothèque minimaliste, afin de fournir un système de type bare metal (en). Il a d'abord été testé sur les cartes de Sipeed, Longan Nano et Wio Lite, et leur processeur GigaDevice GD32V en raison de la possibilité d'accéder facilement à ce type de matériel avec son écran pour moins de 10 €. L'auteur prévoit de le porter également vers l'HiFive1 Rev B[26]. Le même auteur à également produit un interpréteur Forth bare metal pour RISC-V[27].

Cette architecture est supportée en par le noyau Linux via un ensemble de patchs ainsi que par FreeBSD[28]. Son intégration dans le tronc commun stable de Linux est effective depuis la version 4.15, avec un support plus étendu depuis la version 4.17.

Le langage de script MicroPython, version adaptée aux microcontrôleurs de Python, a été porté en 2017 par Microsemi sur architecture RISC-V[29].

Arduino fonctionne sur les microcontrôleurs GD32V de GigaDevice. Il peut utiliser pour cela le système temps réel RT-Thread et l'interface graphique RTT-GUI d'Arduino[30].

Le système temps réel Zephyr fonctionne également sur les processeurs RISC-V, notamment sur son émulation par Qemu et sur différentes implémentations matérielles[31].

La version minimum de Rust à destination de l'embarqué (Minimum Supported Rust Version (MSRV)) est portée sur RISC-V, par la communauté de rust-embedded[32]. Le système RustOS, basé sur un noyau rCore, une version Rust de uCore OS Plus fonctionne sur l'implémentation Qemu de RISC-V et sur les systèmes HiFive Unleashed, et sont utilisés à l'université Tsinghua pour les cours de système d'exploitation[33]

La société UltraSOC développe « Tessent Embedded Analytics » une solution d'analyse et de traçage sur RISC-V, pour les solutions propriétaires ou ouvertes. Elle est rachetée par le groupe Siemens et continue cette activité au sein du groupe[34].

Cette architecture est supportée par les systèmes d'exploitation pour internet des objets, LiteOS (licence BSD) et pour plateformes mobiles HarmonyOS de Huawei[10].

Le logiciel d'aide à la découverte de failles de sécurité, afin de pouvoir les exploiter[35], du service de renseignement des États-Unis, NSA, Ghidra, supporte le format binaire de cette architecture[36].

En , Alibaba fait une démonstration d'Android 10 porté par T-Head sur leur SoC ICE EVB comportant 2 cœurs RISC-V 64 bits XuanTie C910, un cœur vectoriel XuanTie C910V et un GPU Vivante GC8000UL[37].

Systèmes d'exploitations pour serveur et postes de bureau

Différentes distributions Linux sont disponible, dont Debian Bullseye avec plus de 95 % des paquets portés[38], Fedora[39], Ubuntu[40], Yocto[41]. Les systèmes d'exploitation FreeBSD[42] et Haiku[43] bootent également sur RISC-V.

Linux et Haiku peuvent bénéficier de l'accélération des cartes graphiques AMD Radeon HD via le pilote libre Mesa qui est indépendant de l'architecture du processeur[44],[45].

Émulateurs logiciels

Il est possible de simuler ces architectures via différents émulateurs et hyperviseurs.

L'hyperviseur QEMU, ainsi que par ANGEL (un simulateur RISC-V en HTML5 et JavaScript) ou via les cartes ZedBoard et Zybo comportant des FPGA Xilinx Zynq[46],[47]. L'émulation de RISC-V (32 et 64 bits) est supportée nativement dans Qemu à partir de la version 2.12.0 sortie le [48]. La version 5.1 ajoute le support du choix du bios dans les arguments[49].

TinyEMU de Fabrice Bellard (également auteur de QEMU et ffmpeg) est un émulateur léger RISC-V, il est utilisé pour le portage de Haiku (remake libre de BeOS)[50]. Il est également utilisé dans BareDoom, un port de Doom sur RISC-V via Barebox, cette version de TinyEMU étant elle même recompilée en WebAssembly (WASM) pour fonctionner dans un navigateur[51].

Juice-VM est un émulateur de machine virtuelle RISC-V RV64IMASU minimaliste, supportant MMU et entrées/sorties UART. Il permet de faire fonctionner FreeRTOS et également, sur des systèmes très limités en ressources, telles que les microcontrôleurs type ESP32 Xtensa double-cœur avec 8 Mo de PSRAM et 2 Mo de flash SPI, le noyau Linux 5.0 compilé pour architecture RISC-V[52],[53].

RISC-V Rust est un émulateur RISC-V développé en langage Rust et fonctionnant en WebAssembly. Le but étant d'utiliser l'émulateur dans un navigateur. Les systèmes d'exploitation GNU/Linux et xv6-riscv fonctionnent dessus[54].

Implémentations matérielles

Outils de développement

Wrap-V est un générateur de cœurs RISC-V, supportant également l'architecture MIPS en TL-Verilog (Transaction-Level Verilog) et passant par le processeur de macros M4. Il permet de développer des cœurs dont les pipelines comportent 1 à 7 niveaux. Il est possible de modifier la sortie M4 pour l'adapter à des besoins spécifiques. Il est également possible d'utiliser TL-Chisel[55].

Implémentations libres

Le microprocesseur libre LowRISC, est un projet d'implémentation libre et ouverte de RISC-V, créé par Andrew Huang (du MIT, également auteur de la plate-forme ouverte Novena), Julius Baxter (projet OpenRISC et université de Cambridge), Michael B. Taylor (université de Californie à San Diego, UCSD Center for Dark Silicon), Dominic Rizzo (Google ATAP (en)), Krste Asanović (Université de Californie à Berkeley).

Le NEORV32 est une implémentation libre (licence BSD clause 3) d'un SoC, de type microcontrôleur pour FPGA écrit en VHDL, indépendant des plateformes. Il est compatible avec les spécifications 2.2 de RISC-V pour RV32 et passe le test de conformité. FreeRTOS a été porté sur ce SoC[56],[57]. Il se base sur le travail que les développeurs avaient fait pour le neo430, une implémentation d'un processeur FPGA de type microcontrôleur compatible avec le MSP430 de Texas Instrument[58],[59].

Le PicoRV32 est une implémentation libre, sous licence ISC, supportant les jeux d'instructions RV32IMC dont le but est d'avoir la plus petite empreinte possible, avec selon les choix entre 750 et 2000 LUT et une fréquence maximum de 250 à 450 MHz. Il a pour finalité d'être un processeur auxiliaire sur FPGA ou ASIC. Il peut être configuré comme cœur RV32E, RV32I, RV32IC, RV32IM, ou RV32IMC[60] (voir la section #Nomenclature des extensions).

Western Digital propose un gamme de coeurs nommés SweRV, open source, disponibles via CHIP Alliance. Ils ont aussi annoncé une coopération avec Codasip afin de proposer un support commercial de ces coeurs[61]. Ces processeurs hautes performances visent les domaines embarqués et supportent le jeu d’instruction RV32IMC. La famille SweRV se décline comme suit:

- Le Coeur superscalaire SweRV EH1 possède 2 files d'execution et est basé sur un pipeline de 9 étages.

- Le Coeur superscalaire multi-threadé SweRV EH2[62] permet de gérer 2 threads simultanément avec 9 étages de pipeline.

- Le Coeur SweRV EL2 simple issue avec 4 étages de pipeline.

L'Académie chinoise des sciences a rendu publique le processeur Xiangshan, sous licence libre (license Mulan v2, approuvé par l'OSI), le sur Github[63]. Le processeur est développé en langage Chisel, qui d'après les développeurs comporte 5 fois moins de lignes de code qu'en Verilog et permet un développement plus rapide[64],[65]. Au moment de sa sortie, le processeur supporte la distribution Debian Bulleseye pour RISC-V. Une première implémentation matérielle sort en , baptisée Yanqihu, gravée en 28nm et fréquencée entre 1.2 et 1.3 GHz, elle à des performances par GHz similaire aux ARM Cortex-A72 avec 7/Ghz SPEC CPU 2006. Une seconde version prévue pour l'automne de la même année appelée Nanhu, gravée en 14nm et fonctionnant à 2 GHz, devrait atteindre des performances par GHz similaires à un Intel i9-10900K (11.08/Ghz) avec 10/Ghz SPEC CPU 2006, et une puissance de calcul, à cette fréquence, comparable à celle d'un ARM Cortex-A76[66],[65].

Implementations RISC-V propriétaires

SiFive, une startup annonce en , le SiFive U5 Coreplex, utilisant l'architecture RISC-V et permettant d'implanter jusqu'à huit cœurs U54 par SoC, comprenant chacun du cache instruction et données de 1er niveau, le SoC contient un plus large cache de 2e niveau. Le but va être d'implémenter d'abord des versions pour du matériel très spécifique n'ayant pas besoin de beaucoup de puissance, mais de fonctions spécialisées dans un premier temps, pour pouvoir améliorer les technologies par la suite[67].

.png.webp)

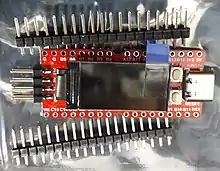

En 2018, la startup SiFive, créée par des développeurs de RISC-V, présente au FOSDEM la carte HiFive Unleashed, comportant un processeur SiFive Freedom U540 SoC (4+1 cœurs RISC-V jusqu'à 1,5 GHz) et 8 Gio de RAM ECC, port ethernet Gb, et capable de faire tourner GNU/Linux[68].

Shakti est une initiative indienne de conceptions de différents processeurs basés sur l'architecture RISC-V et divisés en 6 séries : E-class pour l'embarqué, C-Class pour les microcontrôleurs, I-Class pour les microprocesseurs pour clients légers, M-Class pour la bureautique, S-Class pour les stations de travail et les serveurs, et enfin H-Class pour les super-calculateurs[69].

Codasip est la première société à avoir développé un coeur compatible RISC-V non-libre en (Codix)[70] et a poursuivi son offre avec des familles de coeurs pour l’embarqué et les domaines applicatifs. Les coeurs développés par Codasip sont écrits en CodAL, un langage de description d’architecture. L’outil Studio est utilisé pour obtenir les simulateurs ainsi que les fichiers nécessaires à l’implementation physique de ces coeurs.

La famille L regroupe des coeurs 32-bits basse consommation, visants les domaines de l’embarqué, proposants en option une unité de calculs flottants. Cette famille se décline en 3 ou 5 étages de pipeline.

La famille H regroupe des coeurs hautes performances 64-bits visants les domaines embarqués, propose en option une unité de calculs flottants.

La famille A regroupe des coeurs 64-bits en mesure d’executer Linux, avec l’option de les augmenter de l'extension “P”. Ces coeurs ont 7 étages de pipeline, une unité de calculs flottants, une MMU. De plus les version -MP intègrent des mémoires caches de niveau 1 (L1) et 2 (L2) et supportent jusqu’à 4 coeurs par cluster[71].

Le cœur RISC-V mis à disposition dans Codasip Studio est destiné à l’apprentissage ou des essais[72].

Le concepteur russe Syntacore prévoit de développer, à la demande du conglomérat national Rostec, un processeur RISC-V 8 cœurs en 12nm d'ici à 2025[73].

Embarqué et microcontrôleurs

Lors du 7e RISC-V workshop, Western Digital a annoncé que la compagnie allait développer des processeurs RISC-V. Le but de Western Digital est d'entamer une transition vers des solutions open-source pour ses serveurs de stockage. À terme, WD espère vendre près de deux milliards de processeurs RISC-V par an.

En 2018, la startup grenobloise fabless GreenWave, présente le GAP8, un processeur basse consommation pour IoT, optimisé pour l'intelligence artificielle[74].

En 2019, GigaDevice Semiconductor lance la série de microcontrôleurs GD32V, basé sur la version 32 bits de l'architecture. Parmi les 14 déclinaisons, le GD32VF103 est cadencé à 108 MHz et accède à sa mémoire flash intégrée sans wait states (en), donc sans latence. Il comporte 128 Kio de mémoire flash intégrée à la puce, et 32 Kio de SRAM, 2 convertisseurs analogique-numérique 12 bits et 2 numérique-analogique 12 bits, ainsi que différentes interfaces de communications (3 SPI, 2 I2C, 3 USART, 2 UART, 2 I2S, 2 CAN et 1 USB OTG)[75]. La puce est compatible broche-à-broche avec ses microcontrôleurs GD32 basés sur l'architecture ARM[76], ainsi que le STM32 de STMicroelectronics[77], permettant ainsi de porter facilement les applications d'une architecture à l'autre[76] et également compatible Arduino[30]. Des GD32V sont notamment utilisés dans la carte de développement Sipeed Longan Nano.

Sipeed a également développé la carte Sipeed M1 (ou Kendryte KD233), équipée d'un SoC Kendryte K210 comportant 2 cœurs RISC-V 64 bits et un processeur d'intelligence artificielle. Ces cartes sont prévues pour fonctionner avec FreeRTOS[78]. Cette carte utilise MAIXPy, une version adaptée de MicroPython, programmable via Plateform.IO. Différentes déclinaisons existent, comme MaixDuino, dont la carte à un format compatible avec l'Arduino, et supporte l'IDE[79]. Il est également possible de l'utiliser avec un système d'exploitation Linux. D'autres versions, plus compactes sont déclinées. En Canaan sort le Kendryte K510, une version améliorée comportant une partie microprocesseurs composée de 2 cœurs RV64 et un accélérateur composé d'un autre RV64 avec extension DSP[80].

En 2019, le président des États-Unis, Donald Trump menace de blocage les fournisseurs de Huawei, dont font partie des fondeurs tels que TMSC, et la société britannique ARM, qui fournissaient jusqu'alors l'IP des cœurs utilisés dans les processeurs HiSilicon de Huawei. La société américaine Nvidia ayant racheté au japonais SoftBank les droits sur la société ARM, Huawei a dû trouver une solution de contournement et semble s'être tourné vers RISC-V. Les premiers kits de développements HiHope HiSpark Wifi IoT utilisent un microcontrôleur Hisilicon Hi3518, compatible avec ses nouvelles plateformes, Huawei LiteOS et HarmonyOS. Les compilateurs fournis avec sont des compilateurs GCC à destination de codes d'architecture RISC-V 32 bits[10].

En , Espressif annonce la disponibilité d'un nouveau modèle de NodeMCU basé sur le processeur ESP32-C3, d'architecture RISC-V[81].

Modules réseaux

OpenWifi, présenté en , est une pile WiFi open source, compatible Linux, qui peut fonctionner sur FPGA, une implémentation fonctionnelle a été effectuée sur FPGA Xilinx, connecté à une carte RF fmcomms2/fmcomms4[82]

Les modules BL602/BL604 de Bouffalo Lab, basés sur du RISC-V 32-bit (cœur SiFive E2-Series[83]), sont des modules WiFi & Bluetooth 5.0 LE. Sipeed et Pine64 devraient les intégrer dans leurs cartes à destination de l'IoT[84].

En , Espressif annonce, la sortie du ESP32-C3, WiFi & BLE, un processeur dans la lignée de l'ESP32, mais compatible broche à broche avec l'ESP8266, et utilisant l'architecture RISC-V 32 bits au lieu de Xtensa LX6. Il comporte un processeur cryptographique, mais pas de DSP contrairement à l'ESP32[85].

Spatial

L'agence spatiale européenne développe un processeur neuronal baptisé « NOEL-V » et basé sur l'ISA RISC-V et son extension vectorielle (V ou RVVE) utilisant des technologie RHBD (Radiation Hardened By Design), pour les contraintes de l'environnement spatial (température et rayons ionisants), ainsi que les contraintes d'efficacité énergétique, au cœur de satellites. Le projet est mené par Cobham Gaisler, au Centre européen de recherche et de technologie spatiales (ESTEC), qui avait déjà produit en 2019, un processeur similaire appelé « LEON » basé sur l'architecture SPARC-V8 à la fin des années 1990[86],[87].

Divers

Pinecil de Pine64 est un fer à souder à régulation électronique, basé sur un processeur RISC-V RV32IMAC « Bumblebee Core » à 108 MHz[88].

Sipeed RV-Debugger Plus est un connecteur UART (série) et débugueur JTAG open source, basé sur le SoC Bouffalo Lab BL702, utilisant un microntrôleur RISC-V 32 bits (basés sur les SiFive E2-Series[83]) à 144 Mhz, comportant un FPU, un module de chiffrement, l'Audio (I2S master/slave), il gère le Zigbee 6, Bluetooth 5.0 LE, WiFi et ehternet. Le firmware est un logiciel libre, il est également possible de l'utiliser comme carte de développement[89].

FPGA

ZedBoard et Zybo comportant des FPGA Xilinx[46].

La carte en matériel libre, LicheeTang, de LicheePi, présentée en , carte utilisant un microcontrôleur basé sur l'architecture RISC-V et utilisant un FPGA, utilise un Anlogic EG4S20. Elle comporte des GPIO afin de pouvoir y connecter différents types d'éléments électroniques[90].

La carte Tang Nano FPGA, présentée en , de Sipeed, utilise quant à elle un FPGA GOWIN Semi GW1N de sa famille LittleBee family[91].

La série de cœurs de processeurs Hummingbird E200 (ou HBird E200) est une implémentation chinoise open-source de RISC-V et comprend des implémentations FPGA[92].

En , OpenWiFi est présenté. C'est une pile WiFi matérielle et logicielle libre fonctionnant sur FPGA, avec une implémentation sur Xilinx[82].

En , Efinix propose 3 architectures 32 bits RISCV32I optimisées pour le FPGA Trion[93]

En , est présentée la carte open-source SAVVY-V basée sur le SOC 64 bits PolarFire[94]. Le PolarFire SoC Icicle utilise un SoC en FPGA comportant 5 cœurs 64 bits, dont un RV64IMAC et quatre RV64GC et équipé de 2 Gio de RAM LPDDR4, d'abord présenté en , il sort finalement au 3e semestre 2020[95]. PolarBerry est une variante également proposée en crawdfunding en [96].

SBC

Différentes cartes de type SBC, et fonctionnant sous Linux, sont présentées à partir de 2018, tentant de se fixer un prix similaire aux populaires Raspberry Pi : La SBC HiFive Unleashed (en) est présentée en , basée sur un SoC comportant quatre cœurs U54 RV64GC (64 bits) à 1,5 GHz et 8 Gio de RAM ECC de type DDR4, sur la base d'un financement participatif[97].

Imagination Technologies et le laboratoire RISC-V International Open Source (RIOS) se sont associés pour faire une carte de type SBC appelée PicoRio, dévoilée en au RISC-V Global Forum, la plateforme est globalement open source, à l'exception de certaines parties essentielles comme les I/O ou les accès mémoire[98].

En , Sipeed annonce une SBC utilisant un SoC AllWinner, simple cœur, composé d'un XuanTie C906 (RV64GCV) à 1 GHz en 22 nm, fait par les concepteurs du processeur 16 cœurs RISC-V 64 bits, XT910 d'Alibaba, il n'a pas de GPU 3D, mais un GPU 2D, et un décodeur vidéo matériel, H.264 et H.265, de 64 Mio à 256 Mio de RAM soudée (et certains modèles pourraient avoir de la RAM externe), ainsi que des connexions HDMI, ethernet Gb, USB et USB OTG[99]

En , la SBC BeagleV utilise un SoC StarFive JH7100 comportant un processeur RISC-V double-cœur SiFive U74, un DSP Vision DSP Tensilica-VP6, un moteur NVDLA (architecture ouverte NVIDIA Deep Learning Accelerator) et un moteur de réseau neuronal pour l'accélération d'IA. Sa première déclinaison n'a pas de processeur géométrique 3D, la seconde version comportera un GPU d'Imagination Technologies (donc sans pilote ouvert). Enfin, le SoC comporte un VPU, capable de décoder du H.264 et H.265 jusqu'à 4Kp60, ou bien deux flux en 2Kp30. La carte est équipée de 4 ou 8 Go de RAM en LPDDR4, de 4 ports USB 3.0, d'un port ethernet 10Gb, HDMI 2.0, DSI, deux ISP, un port 40 broches et alimenté par USB-C[100]. Deux versions sont mises à disposition, une comportant 4 Go de RAM à 100$ et une avec 8 Go à 150$, les processeurs gravés en 7 nm par TSMC, tournent à 3.5 GHz, sont de type RV64GCVBH (avec notamment une unité vectorielle) et un processeur obtient des performances aux ARM Cortex-A76 et A77[101],[102]. En , est proposé la distribution Fedora comme distribution par défaut, avec les premières cartes disponibles pour les développeurs. XFCE est le gestionnaire de fenêtre par défaut, pouvant s'afficher sur la sortie HDMI[103].

En , Pine64, annonce, la sortie d'une SBC de développement, basé sur un SoC comportant un cœur RV64GCV (XuanTie C906) et un second RISC-V 32bit BL602 (ESP32-C), pour la partie réseau sans fil, des pilotes ouverts étant en cours de développement pour celui-ci. Le but étant de se fixer un prix inférieur à 15 (US)$, afin de rendre la plateforme de développement accessible au plus grand nombre[104].

Ordinateurs portables

L'Académie chinoise des sciences annonce en , qu'elle est en train de préparer la sortie de 2 000 ordinateurs portables basés sur des RV64GC d'ici la fin 2022 et pour cela travailler à l'optimisation pour RISC-V des moteurs de Firefox (spiderMonkey et son compilateur à la volée (JIT)) et de Chrome/Chromium (WebKit) afin qu'ils y fonctionnent correctement[105].

Serveurs

Le groupe Alibaba a conçu le XuanTie 910 (ou XT910), un SoC à destination des serveurs, composé de 16 cœurs RISC-V 64 bits RV64GCV, organisé en grappes de 4 cœurs comportant 32 ou 64 kb de cache de données et autant en cache d'instruction. Le groupe proclame que les performances d'un cœur sont du même ordre que celles d'un ARM Cortex-A73[106].

Supercalculateurs

L'union européenne a lancé un projet de supercalculateur basé sur l'architecture RISC-V, appelé European Processor Initiative (EPI), financé par le programme EU horizon 2020, développé par 26 partenaires (dont la RISC-V Foundation, le Centro Nacional de Supercomputación (CNS ou BSC), le CEA, Infineon ou encore STMicroelectronics) de 10 pays. Un SoC utilisant l'architecture RISC-V pour les accélérateurs également développés en Europe, a pour but de produire un supercalculateur exascale, ainsi que de fournir le domaine de l'automobile, basé sur des technologies européennes. L'utilisation d'architecture ARM comme processeur principal est envisagée mais pas certaine, dans ce cas RISC-V se limiterait aux accélérateurs de calcul. Le projet cherche à réutiliser les systèmes existants (déjà implémentés sous GNU/Linux)[107].

Annexes

Notes et références

- (en) « RISC-V: An Open Standard for SoCs », EETimes (consulté le )

- (en) Lucian Armasu, « Big Tech Players Start To Adopt The RISC-V Chip Architecture », sur Tom's Hardware,

- (en) Lucian Armasu, « Nvidia Job Listings Point to Ambitious RISC-V Plans », sur Tom's Hardware,

- (en) William G. Wong, « The Rise of RISC-V on Display at Workshop », sur ElectronicDesign,

- (en) Chris Williams, « Up in arms! Arm kills off its anti-RISC-V smear site after own staff revolt », sur The Register,

- (en) Joel Hruska, « ARM Kills Its RISC-V FUD Website After Staff Revolt », sur ExtremeTech,

- (en) Nathaniel Mott, « TSMC Doesn't Want to Make Its Chips in the US », sur Tom's Hardware,

- (en) Nathaniel Mott, « Report: RISC-V Plans to Move From the US to Switzerland », sur Tom's Hardware,

- « RISC V déménage en Suisse pour échapper à la guerre commerciale sino-américaine », sur 01Net

- (en) Jean-Luc Aufranc, « Hi3861 based HiSpark WiFi IoT development board supports LiteOS and HarmonyOS », sur CNX-Software,

- (en) Gareth Halfacree, « René Rebe Patches the Linux Kernel for "World's First" Look at a Radeon RX 6700XT on a RISC-V PC », sur hackster.io,

- (en) « BOOM Open Source RISC-V Core Runs on Amazon EC2 F1 Instances », sur CNX Software,

- (en) Jean-Luc Aufranc, « RISC-V Bases and Extensions Explained », sur CNX-Software,

- Waterman et Asanović 2019, p. 35.

- Jim Ledin, « The RISC-V Architecture », sur DZone,

- (en) Andrew Waterman et Krste Asanović, The RISC-V Instruction Set ManualVolume I: User-Level ISA Document Version 2.2, CS Division, EECS Department, University of California, Berkeley, (lire en ligne), p. 27

- (en) chap. 5 « RV64I Base Integer Instruction Set, Version 2.1 », dans RISC-V Instruction Set Manual, Volume I: RISC-V User-Level ISA , 20191214- December 2019, (lire en ligne)

- (en) RISC-V "V" Vector Extension (lire en ligne)

- (en) Jon Peddie, « RV64X: A Free, Open Source GPU for RISC-V », sur EETimes,

- (en) Jean-Luc Aufranc, « Think Silicon NEOX|V is the First RISC-V ISA based GPU », sur CNX-Software,

- (en) « Kazan », sur salsa.debian.org

- (en) « Download - RISC-V », sur riscv.org consulté le=17 août 2014

- Alicia Daleiden, « Rust Comes to RISC-V », sur Riscv.org,

- Andrew Back, « Rust Comes to RISC-V », sur ABopen,

- https://bronzebeard.readthedocs.io/en/latest/

- (en) « Minimal ecosystem for bare-metal RISC-V development in python », sur Python Awesome.com,

- https://github.com/theandrew168/derzforth

- « [base] Revision 295041 », sur svnweb.freebsd.org (consulté le )

- « RISC-V Poster Preview — 7th RISC-V Workshop », (consulté le )

- (en) « Gd32v », sur Arduinolibraries.info

- (en) « Zephyr », sur RISC-V getting started guide (sur readthedocs.io)

- (en) « Minimum Supported Rust Version (MSRV) », sur Comtpe Rust embedded sur Github

- (en) oscourse-tsinghua sur Github, « rCore »

- (en) « RISC-V is an open source instruction set architecture paving the way for the next 50 years of computing design and innovation. », sur tessentembeddedanalytics.com

- (en) « Ghidra Software Reverse Engineering Framework », sur Github

- (en) « "ghidra/Ghidra/Processors at Ghidra_9.2_build" », sur Code siource de Ghidra sur Github, (consulté le )

- (en) Jean-Luc Aufranc, « Android 10 ported to RISC-V board powered by Alibaba T-Head XuanTie C910 Processor », sur CNX-Software,

- (en) « RISC-V », sur Debian.org

- https://fedoraproject.org/wiki/Architectures/RISC-V

- (en) « Ubuntu 20.04/21.04 64-bit RISC-V released for QEMU, HiFive boards », sur CNX Software,

- https://github.com/riscv/meta-riscv

- https://wiki.freebsd.org/riscv

- https://discuss.haiku-os.org/t/my-haiku-risc-v-port-progress/10663

- https://discuss.haiku-os.org/t/my-progress-on-real-risc-v-hardware/10963/30

- https://www.youtube.com/watch?v=wHp-UIGov8c

- (en) « Getting Started with RISC-V », sur riscv.org (consulté le ), archive

- (en) « riscv-tools », sur riscv.org (consulté le )

- (en) « ChangeLog/2.12 - RISC-V », sur qemu

- (en) « QEMU System Emulation User’s Guide », qemu (consulté le )

- (en) « My Haiku RISC-V port progress », sur Haiku-os.org

- (en) a3f, « bareDOOM », sur BareDoom sur Github

- (en) « JuiceVm », sur compte juiceRv sur Github

- (en) « Linux 5.0 shown to boot on ESP32 processor », sur CNX-Software,

- (en) « riscv-rust », sur Github

- Abhishek Jadhav, « WARP-V: A RISC-V CPU Core Generator Supporting MIPS ISA », sur CNX-Software

- « The NEORV32 RISC-V Processor »

- (en) « The NEORV32 Processor (RISC-V) », sur OpenCores.org

- « The NEO430 Processor », sur Github

- (en) Gareth Halfacree, « Chinese chip designers hope to topple Arm's Cortex-A76 with XiangShan RISC-V design Permissively licensed, the processor's second iteration targets 2GHz at 14nm », sur The Register,

- (en) « PicoRV32 - A Size-Optimized RISC-V CPU », sur GitHub

- « Codasip facilite les implémentations matérielles du cœur open source RISC-V SweRV Core de Western Digital », sur www.lembarque.com (consulté le )

- « Codasip étend la prise en charge des cœurs RISC-V SweRV de Western Digital à des modèles conçus pour l'embarqué », sur www.lembarque.com (consulté le )

- « OpenXiangShan/XiangShan », sur Compte OpenXiangShan sur Github

- (zh) 包云岗, « 首届 RISC-V 中国峰会 2021 年 6 月 21 日起在上海举行,有什么值得关注的地方? », sur 知乎

- (en) Jean-Luc Aufranc, « XiangShan open-source 64-bit RISC-V processor to rival Arm Cortex-A76 », sur CNX-Software,

- (en) « Chinese Academy of Sciences released the domestic RISC-V processor "Xiangshan", which has successfully run Linux, and will be released in July », sur min.news,

- (en) Nicole Hemsoth, « Startup Takes a Risk on RISC-V Custom Silicon », sur The Next Platform,

- Alasdair Allan, « Is RISC-V Finally Taking Off? », sur Hacksters.io,

- (en) « Processors », sur shakti.org.in

- (en) « Codasip Joins RISC-V Foundation and Announces Availability of RISC-V Compliant Codix Processor IP », sur Design And Reuse (consulté le )

- « Codasip lance 3 processeurs RISC‑V multicoeurs pour IA Edge », sur Electronique-ECI, (consulté le )

- « Codasip offre la possibilité de s’exercer sur une implémentation réelle de processeur RISC-V », sur www.lembarque.com (consulté le )

- (en) Dr. Ian Cutress, « Russia To Build RISC-V Processors for Laptops: 8-core, 2 GHz, 12nm, 2025 », sur Anandtech,

- (en) Jean-Luc Aufranc, « GreenWaves GAP8 is a Low Power RISC-V IoT Processor Optimized for Artificial Intelligence Applications », sur CNX-Software, 27f évrier 2018

- (en) GigaDevice Semiconductor Inc, GD32VF103 User Manual, , 533 p. (lire en ligne)

- Gerhard Steizer, « RISC-V for everybody », sur Elektronknet.de,

- (en) Jean-Luc Aufranc, « GigaDevice GD32 is a Faster, Software and Pin-to-pin STM32 Compatible Cortex M3 MCU », sur CNX-Software,

- (en) Brian Benchoff, « New Part Day: The RISC-V Chip With Built-In Neural Networks », sur Hack a Day,

- Kadionik Patrice, « Maixduino : faites de l’IA sur un processeur RISC-V », Hackable, no 36 mois=janvier, (lire en ligne)

- (en) « Kendryte K510 tri-core RISC-V AI processor deliver up to 3 TOPS », sur CNX Software,

- (en) Jean-Luc AUfranc, « NodeMCU ESP32-C3 WiFi & BLE IoT boards show up for about $4 », sur CNX-Software,

- (en) Jean-Luc Aufranc, « OpenWiFi Open-Source Linux-compatible WiFi Stack Runs on FPGA Hardware », sur CNX-Software,

- (en) « Bouffalo Lab Standardizes on SiFive RISC-V Embedded CPU Core IP for New IoT Products », sur Design & Reuse,

- (en) Jean-Luc Aufranc, « BL602/BL604 RISC-V WiFi & Bluetooth 5.0 LE SoC will sell at ESP8266 price point », sur CNX-Software

- (en) Jean-Luc Aufranc, « ESP32-C3 WiFi & BLE RISC-V processor is pin-to-pin compatible with ESP8266 », sur CNX-Software,

- (en) Gareth Halfacree, « Deep neural networks... IN SPAAACE: Vector-enhanced RISC-V chips could give satellites onboard », sur The Register,

- Di Mascio & Al 2021.

- (en) Gareth Halfacree, « Pine Opens Orders for Its RISC-V-Powered Pinecil Smart Soldering Iron — with Free Breakout Board », sur Hackster.io,

- (en) Jean-Luc Aufranc, « $3.5 RV-Debugger Plus UART & JTAG debug board comes with BL702 Zigbee & BLE RISC-V SoC », sur CNX-Software,

- (en) « LicheeTang Anlogic EG4S20 FPGA Board Targets RISC-V Development », sur CNX Software,

- « $5 Tang Nano FPGA Board Features GOWIN GW1N “LittleBee” FPGA », sur CNX Software,

- (en + zh) « Hummingbird E200 Opensource Processor Core », sur GitHub

- (en) Jean-Luc Aufranc, « Efinix Releases Three RISC-V Software-Defined SoC’s Optimized for Trion FPGA’s », sur Cnx-Software,

- (en) Jean-Luc Aufranc, « PolarBerry is a Compact, Linux-capable RISC-V FPGA SBC and module (Crowdfunding », sur CNX Software,

- (en) Jean-Luc Aufranc, « PUpcoming SAVVY-V Open Source RISC-V Cluster Board Supports 10GbE via Microsemi PolarFire 64-bit RISC-V SoC », sur CNX Software,

- (en) Jean-Luc Aufranc, « PolarBerry is a Compact, Linux-capable RISC-V FPGA SBC and module (Crowdfunding », sur CNX Software,

- (en) Jean-Luc Aufranc, « SiFive Introduces HiFive Unleashed RISC-V Linux Development Board (Crowdfunding) », sur CNX Software,

- (en) Jean-Luc Aufranc, « PicoRio Linux RISC-V SBC is an Open Source Alternative to Raspberry Pi Board », sur CNX-Software,

- Jean-Luc Aufranc, « XuanTie C906 based Allwinner RISC-V processor to power $12+ Linux SBC’s », sur CNX-Software,

- Jean-Luc Aufranc, « $119+ BeagleV powerful, open-hardware RISC-V Linux SBC targets AI applications », sur CNX-Software,

- (en) Chloe Ma, « RISC-V Star Rising from the East – Introducing StarFive », sur riscv.org,

- (zh) « 重磅 », sur Compte Starfive sur Weixin,

- (en) Starfive Tech, « BeagleV Starlight RISC-V Fedora image », sur Gihtub

- (en) PINE64, « February Update: Show and Tell », sur Pine64.org

- (en) Gareth Halfacree, « China's ISCAS to build 2,000 RISC-V laptops by the end of 2022 as nation seeks to cut reliance on Arm, Intel chips », sur The Register, .

- (en) Jean-Luc Aufranc, « More Details about Alibaba XT910 64-bit RISC-V Core », sur CNX Software,

- (en) « How the European Processor Initiative is Leveraging RISC-V for the Future of Supercomputing », sur Inside HPC,

Bibliographie en ligne

- (en) « Specifications », sur riscv.org

- (en) Andrew Waterman et Krste Asanović, The RISC-V Instruction Set Manual — Volume I: Unprivileged ISA, CS Division, EECS Department, University of California, Berkeley, (lire en ligne)

- (en) Andrew Waterman et Krste Asanović, The RISC-V Instruction Set Manual — Volume II: Privileged Architecture, CS Division, EECS Department, University of California, Berkeley, (lire en ligne)

- (en) Krste Asanović (en) et David Patterson, Instruction Sets Should Be Free: The Case For RISC-V, Electrical Engineering and Computer SciencesUniversity of California at Berkeley, (présentation en ligne, lire en ligne)

- (Obsolète) The RISC-V Instruction Set HotChips 25 (2013)

- The RISC-V Software Ecosystem HPCA 2015, Tutorial

- Yunsup Lee, RISC-V “Rocket Chip” SoC Generator in Chisel, UC Berkeley, HPCA, (lire en ligne)

- (en) d0iasm, Writing a RISC-V Emulator in Rust (lire en ligne) (source)

- (en) Hiroaki Kaneko et Akinori Kanasugi, An integrated machine code monitor for a RISC-V processor on an FPGA, SpringerLink, (ISSN 1614-7456, OCLC 1196515116)

- (en) Johannes Geier, Fast RTL-based fault injection framework for RISC-V cores, München, Masterarbeit Technische Universität, (OCLC 1193312286)

- (en) SHAKTI Development Team, RISC-V Assembly Language: Programmer Manual Part I, Madras, SHAKTI Development Team, (lire en ligne)

- (en) Stefano Di Mascio, Alessandra Menicucci, Eberhard Gill, Gianluca Furano et Claudio Monteleone, « On-Board Decision Making in Space with Deep Neural Networks and RISC-V Vector Processors », Journal of Aerospace Information Systems, (DOI 10.2514/1.I010916, présentation en ligne, lire en ligne)

Ouvrages

- (en) Andrew Shell Waterman, Design of the RISC-V Instruction Set Architecture, Berkeley, CA, (OCLC 957714390) (dissertation pour un Ph. D. in Computer Science University of California, Berkeley 2016)

- (en) John L. Hennessy et David A. Patterson, Computer Organization and Design RISC-V Edition, Morgan Kaufmann, , 696 p. (ISBN 978-0-12-812275-4, e-ISSN 978-0-12-812276-1[à vérifier : ISSN invalide])

- (zh-Hans) 胡振波, 手把手教你设计CPU:RISC-V处理器篇, 北京, 人民邮电出版社, , 480 p. (ISBN 978-7-115-48052-1, présentation en ligne)

- (ja) デイビッド・パターソン (David A Patterson) et アンドリュー・ウォーターマン (Andrew Waterman) (trad. 成田光彰 (Narita)), RISC-V原典 (リスクファイブ原典) : オープン・アーキテクチャのススメ, 日経BP, , 224 p. (ISBN 978-4-822292-812)

- Gaétan Kuetche Saadeu, Conception d'un microcontrôleur multi-cores à cœurs RISC-V Initiation à la conception d'un microcontrôleur exploitant les Shields de l'Arduino, Saarbrücken, Éditions universitaires européennes, (ISBN 9786139502493)

- (en) John L Hennessy et David A Patterson, Computer architecture : a quantitative approach, Cambridge, Massachussetts, Elsevier, coll. « Morgan Kaufmann series in computer architecture and design », (ISBN 9780128119068)

- (zh-Hans) 胡振波, RISC-V架构与嵌入式开发快速入门, 北京, 人民邮电出版社, , 354 p. (ISBN 9787115494139)

- (en) Anthony J Dos Reis, RISC-V assembly language, États-Unis, , 149 p. (ISBN 9781088462003)

- (en) Jim Ledin, Modern Computer Architecture and Organization : Learn X86, ARM, and RISC-V Architectures and the Design of Smartphones, PCs, and Cloud Servers, Birmingham, Packt Publishing, (ISBN 978-1-838987-107)

- Shruthi K Muchandi, Enabling Accelerator-SoC Co-design Using RISC-V Chipyard, Charlotte, The University of North Carolina, (ISBN 9781392495506)

- (en) Jing Chen, Hardware acceleration for elementary functions and RISC-V processor, Montréal, McGill University Libraries, (OCLC 1199006597)

- (en) Vladimir Herdt, Daniel Große et Rolf Drechsler, Enhanced Virtual Prototyping: Featuring RISC-V Case Studies, Cham, Springer, (ISBN 978-3-030-54827-8, DOI 10.1007/978-3-030-54828-5)

Magazine

- Kadionik Patrice, « Maixduino : faites de l’IA sur un processeur RISC-V », Hackable, no 36, (lire en ligne)

Liens externes

- http://riscv.org/ — Site officiel

- http://www.eecs.berkeley.edu/Pubs/TechRpts/2014/EECS-2014-146.pdf — Jeu d'instruction de RISC-V et comparaisons avec d'autres architectures similaires.

- https://riscv.org/software-tools/riscv-angel/ — ANGEL, simulateur HTTP de jeu d'instruction RISC-V

- (en) « Analyzing the RISC-V Instruction Set Architecture », sur Adapteva — comparaison entre l'architecture RISC-V (version 32 bits) et l'architecture Adapteva.

- (en) « RISC-V », sur wiki.debian.org Port de Debian sur RISC-V

- (en) « RISC-V Cores and SoC Overview », sur Awesome Open Source — Liste d'implémentations

- Portail de l’informatique

- Portail de l’électricité et de l’électronique

- Portail des logiciels libres