Bus informatique

Un bus informatique est un dispositif de transmission de données partagé entre plusieurs composants d'un système numérique. Le terme dérive du latin omnibus (à tous) ; c'est le sens, d'un usage plus ancien, du terme bus en électronique[alpha 1]. Le bus informatique est la réunion des parties matérielles et immatérielles qui permet la transmission de données entre les composants participants.

Pour les articles homonymes, voir Bus.

On distingue généralement un bus d'une part d'une liaison point à point, qui ne concerne que deux composants qui en ont l'usage exclusif, et d'autre part, d'un réseau, qui implique des participants indépendants entre eux, c'est-à-dire pouvant fonctionner de manière autonome, et qui comprend plusieurs canaux permettant des communications simultanées.

Définition et mise en œuvre

Définition fonctionnelle

Un bus est un système de transfert de données entre plusieurs unités fonctionnelles de traitement de données[alpha 2] par l'intermédiaire d'une voie de transmission commune, dans lequel les composants ne prennent aucune part à la transmission des données entre les autres participants[3].

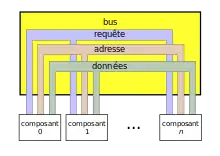

Cette définition implique que les données doivent s'accompagner d'une identification du composant auquel elles sont destinées, qu'on appelle par métaphore l’adresse de destination[4], et d'une commande indiquant le type du transfert, notamment pour indiquer si ce composant doit recevoir les données ou les transmettre. On peut ainsi décomposer le bus en trois sous-ensembles logiques :

- les données, soit le message proprement dit,

- les adresses, qui permettent d'identifier les composants qui partagent les données,

- le contrôle, un ensemble de signaux identifiant le type d'action : lecture ou écriture, taille du message, etc.[alpha 3]

Ces trois groupes sont communément appelés bus (bus d'adresse, bus de données, bus de contrôle). Physiquement, ils peuvent être des bus au sens électronique du terme, c'est-à-dire être portés par des conducteurs indépendants, ou être réalisés d'une autre manière, par exemple par multiplexage temporel sur un seul conducteur ; un bus informatique les combine en un seul dispositif pour transférer des données entre plusieurs composants.

En plus de l'aspect physique permettant de faire transiter les informations, un bus informatique est constitué des circuits d'interface, et du protocole qui définit la manière dont les signaux doivent se comporter pour réaliser ce transfert. Les caractéristiques du matériel conditionnent en partie le type de communication et le protocole peut parfois imposer le type de matériel.

Le débit binaire maximal, exprimé en bits par seconde, décrit la capacité du bus informatique à transférer plus ou moins rapidement des informations.

Autres modes de communication

Lorsque deux composants seulement sont impliqués, le problème de l'adresse ne se pose pas. On parle plutôt de liaison point à point[5],[6]. Un système de transfert de donnée prévu pour plusieurs composants peut effectuer le transfert, mais le traitement inutile de l'information d'adresse pèse sur sa performance.

Lorsque le dispositif de communication comprend plus d'une voie de transmission, permettant plusieurs communications simultanées, la notion de réseau informatique est plus appropriée[7].

Les trois approches, liaison de point à point, bus informatique, réseau informatique, partagent la même fonction de communication, avec une complexité croissante. Elles correspondent à des optimisations particulières à chacun de leurs domaines.

Caractérisation

Les bus informatiques peuvent se construire avec plusieurs variantes.

- Capacité à contrôler le bus

- La désignation des composants concernés et du sens des transferts est souvent le privilège d'un des composants, que l'on désigne sous le nom de maître (Gustavson 1984). Dans le cas où plusieurs composants peuvent contrôler le bus (bus multi-maîtres), celui-ci doit inclure un arbitrage entre les requêtes[8]. Un composant appelé « arbitre de bus » désigne alors quel autre composant est autorisé à en prendre le contrôle, au moyen de différents algorithmes : round-robin, dans lequel le choix du composant est périodique, ou encore en fonction d'une priorité définie par le composant effectuant la requête.

- Requêtes

- Le protocole le plus simple inclut uniquement les requêtes de lecture et d'écriture. Le composant qu'indique l'adresse doit soit copier les données que présente le bus, soit communiquer ses données. Certains bus incluent des fonctions de contrôle qui permettent des transferts plus rapides.

- L'instruction de transfert de bloc ou le burst (en) permettent de demander une transmission non plus d'un seul mot de données, mais de plusieurs successivement de ou vers un bloc d'adresses consécutives, de façon à transférer des blocs de données avec une seule requête. Les signaux de contrôle définissent la taille du bloc. Le transfert de bloc peut doubler le débit numérique du bus[9].

- La fonction read-modify-write (en) permet d'accéder à une donnée, et de bloquer le bus le temps de venir la modifier. Cette fonction est particulièrement utile lors de l'utilisation de données partagées. Si plusieurs composants utilisent les données enregistrées dans les mêmes composants, des conflits d'usage des données peuvent survenir : le composant A lit la donnée à l'adresse a, et commence à effectuer des calculs avec la valeur trouvée. Pendant ce temps, le composant B fait de même. La composant A reprend le contrôle du bus pour venir modifier la donnée de l'adresse a, puis le composant B fait de même. La valeur de sortie du calcul de A est donc perdue. Bloquer le bus pendant le calcul permet de s'assurer que B ne viendra lire la donnée qu'une fois qu'elle a été mise à jour par A, et d'éviter la mise à jour perdue.

- Mode de transmission

- Un bus parallèle transmet simultanément chaque bit constituant le message sur un canal particulier, tandis qu'un bus série les transmet les uns après les autres sur le même canal[alpha 4].

- Synchronisation

- La transmission peut être synchrone, avec un signal d'horloge, ou asynchrone, quand chaque transmission comporte une information de synchronisation. Si la transmission est synchrone, il faut que les différences de temps de transmission dues à la distance entre composants ne dépassent pas la limite permise par le signal d'horloge[alpha 5].

- Topologie

- Dans une topologie linéaire, le bus ressemble à une ligne électrique où sont accrochées, de loin en loin, des lampes ; dans une configuration arborescente, d'un tronc commun sortent des branches et des rameaux en direction des composants. Dans une configuration en anneau deux voies existent d'un composant à un autre. Dans les réseaux complexes, structurés comme des réseaux de télécommunication, les circuits de gestion du bus déterminent le chemin de transmission adéquat, parmi un certain nombre de voies disponibles.

Un bus logiciel est un logiciel d'interface qui permet à un poste d'accéder à des données d'autres composants aussi simplement que s'ils lui étaient reliés par un bus. Ce logiciel décharge les programmes de la sélection des voies et des protocoles de communication. Du point de vue du programme appelant, il n'y a qu'un bus. Du point de vue de l'analyse des systèmes, l'ensemble des voies de communication plus les bus logiciels qui assurent l'interface forme le bus informatique.

Topologies

L'implémentation d'un bus peut suivre différentes topologies[10] selon l'usage qui en est fait et la stratégie d'optimisation : performance, quantité de ressources utilisées, consommation, etc. La topologie influe sur ces facteurs sans affecter les composants connectés. Ceux-ci utilisent en général un protocole générique, et des adaptateurs entre le composant et les ressources de communication permettent la traduction des requêtes en transferts effectifs. Ainsi certaines définitions de bus, comme l'AXI, ne donnent aucune contrainte sur la topologie. Elles indiquent seulement le protocole que les composants doivent utiliser pour accéder au bus, laissant l'implémentation des lignes de communication à la discrétion de l'architecte.

- La topologie historique consiste en un médium de communication partagé par tous les composants. Une seule communication peut avoir lieu à la fois, deux si la lecture et l'écriture utilisent des canaux distincts. Dans le cas d'un bus multi-maître, l'arbitre du bus détermine qui est autorisé à utiliser le bus à chaque instant. Cette topologie présente l'avantage d'utiliser le minimum de ressources, mais peut devenir un goulot d'étranglement en cas de requêtes simultanées.

- La topologie par autocommutateur[11], en grille de commutation matricielle, permet de mettre en œuvre autant de lignes de communications que nécessaire. Un commutateur établit la liaison entre un maître et un esclave, et ne permet la communication qu'entre ces deux composants. Le choix des lignes à établir est réalisé lors de la phase d'implémentation. Ainsi, si un bus est composé de deux maîtres et de plusieurs esclaves, il est possible que l'un des maîtres n'ait jamais à interagir avec certains esclaves. Dans ce cas, il sera inutile de déployer des ressources de communication entre le maître et les esclaves en question. Cette topologie a le grand avantage de permettre à différents maîtres de communiquer simultanément avec des esclaves différents, augmentant les performances. Elle utilise en revanche beaucoup plus de ressources qu'une topologie bus. Si cette topologie se résume, du point de vue implémentation, à un ensemble de lignes point à point, il s'agit néanmoins bien d'un bus car du point de vue des composants, les communications sont effectuées par adresse.

- La topologie Network on Chip s'inspire des réseaux en introduisant de multiples lignes de communication reliées entre elles par des routeurs. Le choix du chemin est réalisé dynamiquement en fonction de l'utilisation des lignes. Cette topologie est adaptée aux SoC comportant de nombreux composants, tels les many-cores (architectures multi-cœur dont le nombre de cœurs est très élevé), et permet plusieurs communications simultanées utilisant différentes liaisons.

Matériel

Dans l'architecture d'un système informatique, les bus transmettent les données entre composants. Les caractéristiques de ces composants déterminent celles du bus. Il est très différent de transmettre des bytes des millions de fois par seconde entre des millions ou milliards de composants très proches les uns des autres, comme c'est le cas entre le microprocesseur et la mémoire d'un ordinateur personnel, des paquets de milliers de bytes en quelques millièmes de seconde entre quelques dizaines de composants éloignés de quelques mètres, comme c'est le cas dans un bus USB, et des codes de quelques dizaines de bits quelques dizaines de fois par seconde, entre des composants dispersés sur un site industriel, comme dans un bus de terrain.

Un bus peut utiliser différents supports pour la communication : fils ou nappes pour relier des périphériques à la carte mère d'un ordinateur (par exemple les bus SCSI ou USB), circuits imprimés sur une même carte ou sur un fond de panier (par exemple dans le cas d'un bus PCI Express), routage logique dans un FPGA (par exemple un bus AXI), fibre optique[12], etc.

Les circuits d'interface, comprenant la conversion parallèle-série et vice-versa, la mémoire tampon et les gestionnaires de communication, ainsi que les répartiteurs et nœuds de communication comme les hubs USB font partie du bus informatique.

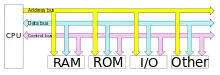

La construction matérielle du bus peut répercuter la représentation logique en trois sous-systèmes physiques, avec des faisceaux de conducteurs distincts pour transmettre les signaux d'adresse, de données et de contrôle, associés à un arbre d'horloge pour la synchronisation. Un bus peut aussi transmettre ces différents signaux l'un après l'autre à travers un seul canal d'une ou plusieurs paires de conducteurs comme c'est le cas de l'USB.

Quand le dispositif est un bus au sens électronique du terme, c'est-à-dire que tous les composants participants sont reliés aux mêmes conducteurs électriques, pour permettre à un composant, que les lignes ou commandes d'adresse et de contrôle désignent parmi plusieurs, de fixer l'état des lignes de données avec des transitions rapides, aussi bien montantes que descendantes, les composants participants utilisent des sorties soit à 3 états, soit à collecteur ouvert[alpha 6],[13]. La fréquence maximale de la communication limite la longueur de ce type de bus. Quand la longueur du conducteur dépasse le quart d'onde de la fréquence maximale dans le conducteur, les phénomènes de réflexions sur les ruptures d'impédance mènent à préférer des lignes de transmission avec répétiteur à chaque node (comme dans l'USB).

Les voies de communication électroniques peuvent être asymétriques, avec le retour du courant par la masse, ou symétriques, avec deux conducteurs d'égale impédance par rapport à la masse. La différence de potentiel, positive ou négative, entre les deux conducteurs constitue le signal. Les canaux symétriques, particulièrement sur paire torsadées, sont moins sensibles aux perturbations, qui agissent à peu près également sur les deux conducteurs, et n'influent pas leur différence.

En général, les systèmes distinguent deux signaux correspondant l'un à 1 et l'autre à 0. Ces signaux peuvent être, dans un bref intervalle de temps déterminé par le signal d'horloge, des niveaux électriques, des transitions entre niveaux[alpha 7] ou bien une transition ou un maintien[alpha 8]. L’élément de signal[14] de la transmission est un bit. Néanmoins, des systèmes peuvent transmettre en distinguant plus de niveaux[15]. Dans ce cas, chaque élément numérique à n niveaux contient bits[16]. Lorsqu'on doit tirer le meilleur parti de lignes de qualité médiocre, on utilise des modulateurs-démodulateurs (modems). Le débit peut alors également s'exprimer en bauds, c'est-à-dire en nombre de signaux échangés par seconde.

Protocole

Le protocole régit la manière dont les échanges sur le bus sont effectués au niveau logique. Par exemple, une première phase peut consister à demander l'accès au bus, suivie d'une deuxième phase consistant à indiquer l'adresse à laquelle on souhaite effectuer une opération de lecture ou d'écriture, puis enfin à transférer ces données. Le protocole détaille l'ordre dans lequel les valeurs doivent être placées sur les différents signaux du bus. Généralement, il peut s'exprimer par un chronogramme représentant les valeurs à donner à différents signaux pour réaliser une opération.

Dans certains types de bus, seul le protocole est défini, et non la nature du médium de transmission, laissée à l'appréciation du concepteur du bus. Par exemple, le protocole AXI définit les interfaces du bus sans se prononcer sur la topologie de celui-ci, qui peut prendre plusieurs formes selon les besoins du système. Ainsi, si le besoin en termes de nombre de communications simultanées est faible, on choisira une topologie de type bus pour économiser des fils, tandis que si certains couples de composants communiquent fréquemment entre eux de manière simultanée, on choisira une topologie crossbar pour éviter les files d'attente. Ce type de bus est particulièrement adapté aux FPGA, pour lesquels la topologie peut être changée en un clic, la mise en œuvre étant laissée au logiciel réalisant la synthèse du circuit.

Approches parallèle et série

Deux grandes catégories de bus peuvent être distinguées selon la manière dont sont transmises les données : tous les bits simultanément, ou un à un.

Bus parallèle

Un bus parallèle transmet simultanément les éléments numériques d'un signal numérique sur un nombre approprié de trajets parallèles entre les composants participants[17].

Matériel

D'un point de vue matériel, ce type de bus se décompose en trois sous-ensembles :

- les lignes de données transmettent les données. À chaque cycle de temps, chaque conducteur transmet un élément numérique. La taille du bus en bits est le nombre de conducteurs de ce sous-ensemble, c'est-à-dire le nombre d'informations (ou bits) que le bus peut transmettre en un seul cycle. Les tailles en bits les plus courantes sont : 8, 16, 32 ou 64 cependant certaines cartes graphiques peuvent avoir des bus de jusqu'à 1 024 bits[18].

- les lignes d'adresse indiquent quel composant doit émettre ou recevoir l'information présente sur les bus de données. Le nombre de conducteurs d'adresse déterminent l'espace adressable du bus. Un bus à n conducteurs d'adresse a un espace adressable de 2n, correspondant au nombre de combinaisons possibles d'états des conducteurs. À chacune de ces combinaisons peut correspondre un composant.

- la ou les lignes de contrôle indiquent quelle est l'opération à effectuer. Lorsque le transfert se fait toujours de ou vers le même composant, il suffit d'une ligne qui indique lecture ou écriture.

Fonctionnement

Le bus sert à transmettre un code binaire d'un nombre de bits égal à la taille du bus. Par exemple pour un bus quatre bits on peut transmettre 16 codes différents (24 = 16).

L'émetteur positionne au même instant tous les bits du bus. Au moment adéquat le composant lecteur copiera tous les bits simultanément. Cet instant adéquat peut être déterminé par un des signaux de contrôle qui changera de valeur pour signaler au dispositif lecteur qu'il est temps de lire les données sur le bus.

Cas d'utilisation

- Lecture et écriture de la mémoire vive par un processeur. Ces bus sont structurés autour de bus au sens de l'électronique, avec leur limitation de longueur. Plus le transfert est rapide, plus ils doivent être courts. Quand l'application exige qu'ils soient plus longs, comme dans le Small Computer System Interface, la cadence de transmission doit être diminuée.

- Interconnexion de disques durs SCSI. Une nappe à 68 conducteurs relie chaque disque à l'adaptateur et transporte tour à tour les signaux de commandes et de données sur 16 bits. Ce type de bus est très rapide quand la nappe est de haute qualité, il peut atteindre 320 Mo/s.

- Connecteurs PCI des cartes d'extension d'un ordinateur personnel, ils permettent des transferts jusqu'à 2 133 Mo/s.

Bus série

Un bus série transmet les éléments numériques d'un signal numérique successivement par un seul trajet entre deux points[19].

Matériel

Un bus série peut comporter deux lignes distinctes permettant à ces bus d'être bidirectionnels et de permettre la transmission d'information dans les deux directions simultanément, plus des lignes auxiliaires pour d'éventuels signaux de contrôle.

Fonctionnement

Le bus série transmettant les données élément par élément, l'émetteur doit sérialiser l'information pour sa transmission. Le récepteur devra effectuer l'opération inverse.

Le composant émetteur doit transmettre un mot de 32 bits. Le protocole du bus précise dans quel ordre il doit les placer, soit en commençant par le bit le plus significatif (MSB), soit par l'autre bout (LSB). Il transforme ainsi le mot en une séquence sur 32 cycles de synchronisation du bus. Le composant récepteur reconstruit le mot de 32 bits à partir des bits reçus.

Le câble de bus série comporte beaucoup moins de conducteurs qu'un bus parallèle, ce qui simplifie le câblage et entrave moins la circulation de l'air dans les appareils informatiques grâce à la réduction de la taille du câble, et à sa souplesse. Un bus série emploie nécessairement des composants électroniques pour la sérialisation.

Certains bus série, tel que le FireWire, utilisent un multiplexage temporel pour transmettre les différentes informations (adresse, contrôle et données). On peut aussi les caractériser comme jonction multiplex[20].

Cas d'utilisation

- Une liaison Universal Serial Bus USB est un bus série ;

- Les disques durs récents utilisent un bus série (FC, PCI, SAS ou SATA). Les débits peuvent ici atteindre plusieurs Go/s.

Systèmes comportant des bus informatiques

La nature des bus utilisés est différente selon le type de système, chacun ayant des besoins et des contraintes propres.

Dans un ordinateur

Les bus situés à l'intérieur d'un même ordinateur relient ses différentes parties fonctionnelles.

Le débit binaire d'un bus est le produit de la fréquence maximale à laquelle un transfert peut avoir lieu par le nombre de bits d'information qu'il peut transmettre simultanément.

Ce calcul vaut pour les bus parallèles. Les bus série doivent transmettre, en plus de la donnée, des signaux qui indiquent le début d'une séquence, et le plus souvent des informations d'adresse et de contrôle. S'ils sont asynchrones, il faut ajouter encore des informations de synchronisation. Ils peuvent comprendre en outre des informations redondantes, Somme de contrôle ou Contrôle de redondance cyclique, pour permettre la détection d'erreur. On les caractérise uniquement par le débit binaire.

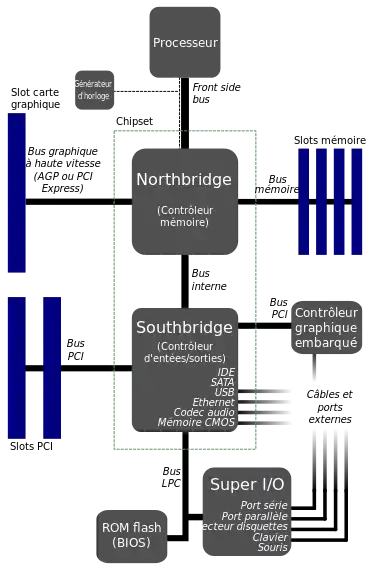

Bus internes

Les bus internes, également connus sous le nom de bus de données, bus mémoire, système de bus ou de front-side-bus, relient les composants internes principaux d'un ordinateur, tels que le processeur et la mémoire, sur la carte mère. Le bus de données interne est également considéré comme un bus local, parce qu'il est destiné à se connecter à des périphériques locaux. Ce bus est généralement assez rapide et est indépendant du reste des opérations informatiques.

Habituellement les bus internes en lien avec l’extérieur d'un microprocesseur d'ordinateur personnel sont au nombre de deux[21] :

- Le northbridge

- qui le relie aux périphériques rapides tels que la mémoire, et les cartes graphiques PCI[alpha 9] ;

- Le southbridge

- qui le relie à tous les périphériques internes plus lents et le bus PCI ;

- Le bus PCI

- utilisé pour effectuer la connexion entre le southbridge et tous les périphériques externes (disques durs, imprimante, etc.). Depuis 2004, le bus PCI Express est utilisé pour les périphériques rapides (cartes graphiques et parfois SSD) et connecté au « north bridge » alors que le bus PCI est maintenant connecté au « south bridge » ;

- le bus InfiniBand

- bus haute-vitesse utilisable aussi bien en interne qu'en externe ;

- depuis 2003

- connexion SATA simplifiant le branchement de disque durs/SSD et lecteurs de CD/DVD internes ;

Bus externe

Les dispositifs électroniques qui relient l'ordinateur (la carte mère) à différents dispositifs externes, tels que l'imprimante, disque dur, scanner, etc. constituent les « bus externes » ou « bus d'expansion ». Ce sont :

Dans les systèmes embarqués

Les systèmes embarqués nécessitent des bus avec peu de conducteurs afin de minimiser les entrées/sorties nécessaires à leur définition. C'est dans ce cadre que différents standards ont émergé, basés sur une communication série avec un minimum de signaux nécessaires.

Le Serial Peripheral Interface (SPI) propose un bus basé sur quatre fils : un fil d'horloge pour le cadencement, deux fils de données pour les deux sens lecture et écriture, et un fil de sélection du périphérique jouant le rôle de l'adresse. Chaque périphérique disposant de son propre fil de sélection, le maître devra disposer d'autant de fil de sélection qu'il y a de périphériques.

l'I2C est un bus permettant de faire transiter des données en utilisant uniquement deux fils : un pour l'horloge et un pour les données. L'adresse est transmise par le même fil que les données.

Ce type de bus est très facile à mettre en œuvre sur des entrées/sorties généralistes (General Purpose Input/Output, GPIO), ce qui a permis leur généralisation sur des systèmes de type Arduino, accessibles à tous de par leur faible cout et utilisés pour de nombreuses application de contrôle-commande, par exemple en domotique. De nombreux capteurs sont notamment interfacés en utilisant l'une de ces normes.

Au sein d'une puce

Le développement des systèmes sur une puce (system on a chip ou SoC an anglais) a conduit à l'apparition de nouveaux types de bus. Ces systèmes rassemblent au sein d'une même puce différents calculateurs et périphériques qui doivent être interconnectés et communiquer. La nature intégrée et physiquement très rapprochée de ces systèmes annule certaines limitations (notamment liées à la longueur des conducteurs) et, dans certains cas, en développe de nouvelles (comme la surface disponible pour les composants d'interface)[24].

Ces bus n'ayant pas besoin d'être interfacés en dehors de la carte, il devient possible de créer un bus sur mesure pour les besoins du système. Néanmoins, avec la notion de réutilisation des composants, la standardisation de ces bus reste d'actualité. En effet, le développement de composants étant une tâche complexe et couteuse, il s'agit de pouvoir réutiliser de différentes manières la structure d'un composant créé afin de limiter les couts afférents au développement de ceux-ci. On parle d'intellectual property (en), ou IP, pour ces composants réutilisables, parfois distibués sous licence (commerciale ou gratuite). Ces composants disposent donc généralement d'une interface standardisée capable de s'interfacer avec un type particulier de bus, afin de ne pas avoir à redévelopper une interface pour chaque utilisation du composant.

Dans ce contexte, la définition de bus standards pour les SoC est devenue centrale pour permettre la réutilisation. Différents standards ont émergé, tels Advanced Microcontroller Bus Architecture développé par ARM et qui spécifie plusieurs bus destinés à différentes applications, Avalon, développé par Altera, ou encore le bus libre Wishbone. Ces types de bus standardent les interfaces, permettant de faciliter la réutilisation d'IP dans un SoC, tout en laissant à l'architecte système une certaine marge de manœuvre quant à la mise en œuvre de la partie transmission. Ainsi, l'architecte peut dans certains cas choisir la topologie du bus, choisir le type d'arbitrage pour les bus multi-maîtres, etc.

Annexes

Bibliographie

- Commission électrotechnique internationale, « Technologie de contrôle - Unités spécifiques en technologie de commande et de régulation », dans CEI 60050 - Vocabulaire électrotechnique international (lire en ligne), p. 351-56-10 « bus »

- (en) David B. Gustavson, Computer busses : a tutorial, (lire en ligne)

Articles connexes

- Architecture (informatique)

- Bus (électricité)

- Catégorie Bus informatique

- Arbre d'horloge

- Bus logiciel

- Sortie à trois états

Notes et références

Notes

- En électrotechnique, on parle de barre omnibus[1].

- Unité fonctionnelle :« entité prise en considération définie selon sa fonction ou son effet. (…) Une unité fonctionnelle peut être mise en application par une ou plusieurs unités physiques ou modules de programme[2]. ».

- Dans certains cas, notamment de bus de terrain, les composants ne peuvent effectuer qu'une action. Par exemple, les capteurs ne peuvent que transmettre, les actionneurs que recevoir. Dans ce cas, seul l'unité centrale peut transmettre, recevoir et affecter les adresses. La présence de l'adresse sur le bus suffit pour contrôler les autres participants.

- Rien ne s'opposerait à des mélanges entre ces modes de transmission, par exemple un bus parallèle de huit bits transmettant d'abord quatre octets d'adresse, puis huit octets de données ; mais en général, les bus sont soit entièrement série, soit entièrement parallèle.

- Dans le vide, l'information voyage à a vitesse de la lumière, soit 3 × 108 m s−1 ; dans les conducteurs d'un circuit, nettement moins vite (Gustavson 1984, p. 10). Avec une fréquence de bus de 300 MHz le temps permis pour la lecture d'un état du bus est de moins de 1 × 10−9 s, le temps pour le signal de parcourir au plus 30 cm.

- Avec des sorties à collecteur ouvert l'impédance plus élevée pour l'état réalisé par la résistance de charge ralentit la transition vers cet état, empêchant la réalisation de bus rapides.

- Transition montante ou descendante, par exemple Codage Manchester.

- Par exemple le codage Non Return to Zero Inverted.

- Depuis 2004 et la mise en place du bus PCI express, le bus PCI est connecté au « south bridge ».

Références

- 151-12-30 « barre omnibus », CEI 60050

- 351-56-02 Unité fonctionnelle, CEI 60050

- 351-56-10 « bus », CEI 60050.

- 714-21-10 « adresse (en logiciel) », CEI 60050.

- Qu'est-ce qu'un bus informatique ?, sur le site commentcamarche.net, aout 2014

- Definition of:bus, PC mag encyclopedia, consulté le 12 juillet 2014

- CEI.

- Bases d'architectures des systèmes électroniques, (lire en ligne), p. 24 [PDF] ; CEI ; Gustavson 1984, p. 4.

- Gustavson 1984, p. 40.

- (en) Historique des topologies de bus.

- En anglais Crossbar switch (en), Michel Fleutry, Dictionnaire encyclopédique d'électronique : anglais-français, Paris, La maison du dictionnaire, , 1054 p. (ISBN 2-85608-043-X), p. 164.

- 731-08-02 bus optique, CEI 60050.

- Gustavson 1984, p. 8-9.

- 704-16-01 « élément de signal (en transmission numérique) », CEI 60050.

- 704-16-05 « signal numérique n-aire », CEI 60050.

- (en) Digital Transmission (Line Coding), vue 35.

- 731-08-02 « transmission (numérique) (en) parallèle », CEI 60050.

- Le JEDEC pose les bases de la HBM 2, sur le site hardware.fr du 13 janvier 2016, consulté le 28 janvier 2016.

- 731-08-02 « transmission (numérique) (en) série », CEI 60050.

- 704-14-12 « highway », CEI 60050.

- (en) What is north gate and south gate on a motherboard, sur le site answers.com

- Présentation de l'USB et du Firewire, sur le site telecom-lille.fr, consulté le 24 février 2016.

- Disques durs externes: la technologie eSATA, successeur de l'USB?, sur zdnet.fr du 20 décembre 2006 consulté le 18 novembre 2018

- Comparing AMBA AHB to AXI Bus using System Modeling, sur le site design-reuse.com

- Portail de l’électricité et de l’électronique

- Portail de l’informatique