Procédé planar

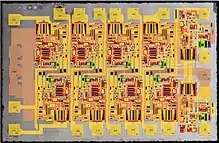

Le procédé planar est un procédé de fabrication utilisé dans l'industrie des semi-conducteurs pour fabriquer les parties élémentaires d'un transistor et connecter ensemble les transistors ainsi obtenus. C'est le processus principal de fabrication des puces de circuits intégrés en silicium. Il utilise les méthodes de passivation de surface et d'oxydation thermique.

Le procédé planar a été développé chez Fairchild Semiconductor en 1959 par Jean Hoerni, qui a adopté les méthodes de passivation de surface et d'oxydation thermique initialement développées par Mohamed Atalla aux Laboratoires Bell en 1957. Puis en 1959, le procédé planar de Hoerni fut à son tour la base de l'invention par Robert Noyce de la première puce de circuit intégré monolithique de Fairchild.

Principe

Le concept clé du procédé planar est de visualiser un circuit dans sa projection bidimensionnelle (un plan), permettant ainsi l'utilisation de concept de traitement photographique tel que les négatifs de films pour masquer la projection de produits chimiques exposés à la lumière. Cela permet d'utiliser une série d'expositions sur un substrat (silicium) pour créer de l'oxyde de silicium (isolants) ou des régions dopées (conducteurs). Avec l'utilisation de la métallisation et les concepts d'isolement de jonction p – n et de passivation de surface, il est possible de créer des circuits sur une seule tranche de cristal de silicium à partir d'un barreau de silicium monocristallin.

Le processus implique les procédés de base d'oxydation de dioxyde de silicium (SiO2), de gravure de SiO2 et de diffusion thermique. La dernière étape consiste à oxyder la totalité de la tranche avec une couche de SiO2, à graver des plots de contact sur les transistors et à déposer une couche métallique de couverture sur l'oxyde, connectant ainsi les transistors sans les câbler manuellement.

Histoire

Contexte

En 1955, Carl Frosch (en) et Lincoln Derick des Laboratoires Bell (BTL) ont découvert par hasard que le dioxyde de silicium pouvait se développer sur le silicium[1]. En 1958, ils ont proposé que les couches d'oxyde de silicium pourraient protéger les surfaces de silicium pendant les processus de diffusion et pourraient être utilisées pour le masquage par diffusion[2],[3].

La passivation de surface, procédé par lequel une surface semi-conductrice est rendue inerte, et ne modifie pas les propriétés des semi-conducteurs suite à l'interaction avec l'air ou d'autres matériaux en contact avec la surface ou le bord du cristal[4], a d'abord été développée par l’ingénieur égyptien Mohamed Atalla à BTL à la fin des années 1950[5],[6]. Il a découvert que la formation d'une couche de dioxyde de silicium à croissance thermique (SiO2) réduit considérablement la concentration des états électroniques à la surface du silicium et a découvert la qualité importante des films de SiO2 pour préserver les caractéristiques électriques des jonctions p-n et empêcher ces caractéristiques électriques de se détériorer par l'environnement ambiant gazeux[3]. Il a découvert que les couches d'oxyde de silicium pouvaient être utilisées pour stabiliser électriquement les surfaces de silicium[2]. Il a développé le processus de passivation de surface, une nouvelle méthode de fabrication des dispositifs à semi-conducteurs qui implique le revêtement d'une tranche de silicium par une couche isolante d'oxyde de silicium afin que le courant puisse pénétrer de manière fiable vers le silicium conducteur placé en dessous. En faisant croître une couche de dioxyde de silicium au-dessus d'une tranche de silicium, Atalla a pu surmonter les états de surface qui empêchaient le courant d'atteindre la couche semi-conductrice[7].

Atalla a publié ses découvertes pour la première fois en 1957[8],[9]. Selon Chih-Tang Sah, ingénieur chez Fairchild Semiconductor, le procédé de passivation de surface développé par Atalla et son équipe était « l'avancée technologique la plus importante et la plus significative, qui a ouvert la voie au circuit intégré en silicium »[10],[11],[12].

Développement

Lors d'une réunion de la Electrochemical Society en 1958, Mohamed Atalla (en) a présenté un article sur la passivation de surface des jonctions PN par oxydation thermique, basé sur ses notes de service BTL de 1957[13] et a démontré l'effet passivant du dioxyde de silicium sur une surface de silicium[9]. Il s'agissait de la première démonstration montrant que des films isolants de dioxyde de silicium de haute qualité pouvaient être développés thermiquement sur la surface du silicium pour protéger les jonctions p-n des diodes et des transistors sous-jacents[3].

L'ingénieur suisse Jean Hoerni a assisté à la même réunion de 1958 et a été intrigué par la présentation d'Atalla. Hoerni est venu avec "l'idée planar" un matin en pensant au dispositif d'Atalla[13]. Profitant de l'effet passivant du dioxyde de silicium sur la surface du silicium, Hoerni a proposé de réaliser des transistors protégés par une couche de dioxyde de silicium. Cela a conduit à la première mise en œuvre réussie du produit de la technique d'Atalla de passivation des transistors au silicium par l'oxyde thermique[14].

Le procédé planar a été développé par Jean Hoerni, l'un des " huit traîtres ", alors qu'il travaillait chez Fairchild Semiconductor, avec un premier brevet délivré en 1959[15],[16].

Avec l'utilisation de la métallisation (pour relier les circuits intégrés) et le concept d'isolement de jonction p – n (de Kurt Lehovec), les chercheurs de Fairchild ont pu créer des circuits sur une seule tranche de cristal de silicium (une plaquette) à partir d’un barreau de silicium monocristallin.

En 1959, Robert Noyce s'est appuyé sur le travail de Hoerni avec sa conception d'un circuit intégré (IC), en ajoutant une couche de métal au sommet de la structure de base de Hoerni pour connecter différents composants, tels que des transistors, des condensateurs ou des résistances, situés sur la même puce de silicium. Le procédé planar a fourni un moyen puissant de fabriquer un circuit intégré qui était supérieur aux conceptions antérieures du circuit intégré[9]. L'invention de Noyce a été la première puce CI monolithique[17],[18].

Les premières versions du procédé planar utilisaient un processus de photolithographie utilisant une lumière en ultraviolet proche émise par une lampe à vapeur de mercure. À partir de 2011, les plus petites structures sont généralement réalisées avec une lithographie UV «profonde» de 193 nm[19]. Certains chercheurs utilisent une lithographie ultraviolette extrême à énergie encore plus élevée.

Voir aussi

Références

- (en) Ross Knox Bassett, To the Digital Age: Research Labs, Start-up Companies, and the Rise of MOS Technology, Johns Hopkins University Press, , 23 p. (ISBN 9780801886393, lire en ligne)

- (en) Christophe Lécuyer et David C. Brock, Makers of the Microchip: A Documentary History of Fairchild Semiconductor, MIT Press, (ISBN 9780262294324, lire en ligne), p. 111

- (en) A. Saxena, Invention of integrated circuits: untold important facts, World Scientific, coll. « International series on advances in solid state electronics and technology », , G97 p. (ISBN 9789812814456, lire en ligne)

- (en) « Surface Passivation - an overview », ScienceDirect, sur sciencedirect.com (consulté le )

- (en) « Martin Atalla in Inventors Hall of Fame », sur invent.org, (consulté le )

- (en) Lachlan E. Black, New Perspectives on Surface Passivation: Understanding the Si-Al2O3 Interface, Springer, (ISBN 9783319325217, lire en ligne), p. 17

- « Dawon Kahng », National Inventors Hall of Fame, sur invent.org (consulté le )

- (en) Bo Lojek, History of Semiconductor Engineering, Springer Science & Business Media, (ISBN 9783540342588), p. 120 et 321–323

- (en) Ross Knox Bassett, To the Digital Age: Research Labs, Start-up Companies, and the Rise of MOS Technology, Johns Hopkins University Press, (ISBN 9780801886393, lire en ligne), p. 46

- (en) Wolf, « A review of IC isolation technologies », Solid State Technology, , p. 63 (lire en ligne)

- (en) Howard R. Huff, H. Tsuya et U. Gösele, Silicon Materials Science and Technology: Proceedings of the Eighth International Symposium on Silicon Materials Science and Technology, Electrochemical Society, (lire en ligne), p. 181-182

- (en) Sah, « Evolution of the MOS transistor-from conception to VLSI », Proceedings of the IEEE, vol. 76, no 10, , p. 1280-1326 (1290) (ISSN 0018-9219, DOI 10.1109/5.16328, Bibcode 1988IEEEP..76.1280S, lire en ligne)

- (en) Bo Lojek, History of Semiconductor Engineering, Springer Science & Business Media, (ISBN 9783540342588), p. 120

- (en) Sah, « Evolution of the MOS transistor-from conception to VLSI », Proceedings of the IEEE, vol. 76, no 10, , p. 1280–1326 (1291) (ISSN 0018-9219, DOI 10.1109/5.16328, Bibcode 1988IEEEP..76.1280S, lire en ligne)

- Brevet US 3025589 Hoerni, J. A.: "Method of Manufacturing Semiconductor Devices” filed May 1, 1959

- Brevet US 3064167 Hoerni, J. A.: "Semiconductor device" filed May 15, 1960

- « 1959: Practical Monolithic Integrated Circuit Concept Patented », Computer History Museum (consulté le )

- « Integrated circuits », NASA (consulté le )

- Shannon Hill. "UV Lithography: Taking Extreme Measures". National Institute of Standards and Technology (NIST).

- Portail de l’électricité et de l’électronique

- Portail des micro et nanotechnologies