NMOS

Un circuit logique MOS de type N utilise des MOSFETs (transistors à effet de champ à structure métal-oxyde-semiconducteur ou MOS) de type n pour fabriquer des portes logiques et autres circuits numériques. Ces transistors nMOS fonctionnent en créant une couche d'inversion dans un transistor à substrat de type p. Cette couche d'inversion, appelée canal n, peut conduire les électrons entre les électrodes "source" et "drain" de type n. Le canal n est créé en appliquant une tension sur la troisième électrode, appelée la grille. Comme les autres MOSFETs, les nMOS ont quatre modes de fonctionnement : bloqué (sous le seuil), linéaire (ou triode), saturation (appelé parfois actif) et saturation en vitesse.

Description

MOS signifie metal-oxide-semiconductor (métal-oxyde-semiconducteur), reflétant la façon dont les transistors MOS étaient fabriqués anciennement, essentiellement avant les années 1970, avec des grilles en métal, typiquement de l'aluminium. Cependant, depuis le début des années 1970, la plupart de circuits MOS utilisent des grilles auto-alignées faites de silicium polycristallin, une technologie développée par Federico Faggin à Fairchild Semiconductor. Ces grilles en silicium sont encore utilisées dans la majorité des types de circuits intégrés basés sur des MOSFET, bien que les grilles en métal (Al ou Cu) aient commencé à réapparaître au début des années 2000 sur certains types de circuits à haute vitesse, comme les microprocesseurs à haute performance.

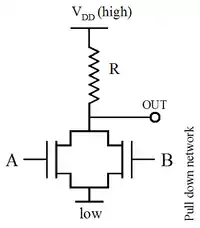

Les MOSFETs sont des transistors de type n à enrichissement, disposés selon un réseau appelé en anglais "pull-down network" (PDN) entre la sortie de la porte logique et la tension d'alimentation négative (typiquement la masse). Une résistance de rappel (c'est-à-dire une "charge" qui peut être vue comme une résistance, voir plus bas) est placée entre la tension d'alimentation positive et chaque sortie de porte logique. Tout type de porte logique, dont l'inverseur logique, peut donc être implémenté en concevant un réseau de circuits parallèle et/ou série, tel que si la sortie désirée pour une certaine combinaison de valeurs d'entrée booléennes est zéro (ou faux), le réseau PDN sera actif, ce qui signifie qu'au moins un transistor permet le passage du courant entre l'alimentation négative et la sortie. Ceci entraîne une chute de tension sur la charge, et donc une tension basse à la sortie, représentant le zéro.

A titre d'exemple, on présente ici une porte NOR implémentée en NMOS schématisé. Si l'entrée A ou l'entrée B est haute (logique 1 = Vrai), le transistor MOS respectif agit comme une très faible résistance entre la sortie et l'alimentation négative, forçant la sortie à être basse (logique 0 = Faux). Quand les deux entrées A et B sont hautes, les deux transistors conduisent, créant une résistance encore plus faible vers la masse. Le seul cas où la sortie est haute se produit lorsque les deux transistors sont bloqués, ce qui se produit seulement lorsque A et B sont bas, et donc respectent la table de vérité d'une porte NOR :

| A | B | A NOR B |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

Un MOSFET peut fonctionner comme une résistance, et donc l'ensemble du circuit peut être fabriqué avec uniquement des MOSFET de type n. Les circuits NMOS sont lents pour passer du niveau bas au niveau haut. Lors de la transition entre les niveaux haut et bas, les transistors offrent une faible résistance, et la charge capacitive en sortie s'élimine très vite (similaire à la décharge d'une capacité à travers une très faible résistance). Mais la résistance entre la sortie et l'alimentation positive est beaucoup plus forte, et donc la transition du niveau bas au niveau haut est beaucoup plus lente (similaire à la charge d'une capacité à travers une résistance de valeur élevée). L'utilisation d'une résistance plus faible accélérera le processus mais accroîtra également la dissipation de puissance statique. Cependant, une meilleure façon (la plus courante) de rendre les portes plus rapides est d'utiliser comme charges des transistors à appauvrissement au lieu de transistors à enrichissement. Ceci est appelé depletion-load NMOS logic (logique NMOS à charge à appauvrissement).

Pendant de nombreuses années, les circuits NMOS furent beaucoup plus rapides que les circuits PMOS et CMOS comparables, qui utilisaient des transistors à canal p beaucoup plus lents. Il était aussi plus facile de fabriquer des NMOS que des CMOS, ces derniers devant comporter des transistors à canal p intégrés dans des puits spéciaux de type n dans le substrat de type p. Le plus grand défaut des NMOS (et de la plupart des autres familles logiques) est qu'un courant continu doit traverser une porte logique même si la sortie est dans un état constant (bas dans le cas des NMOS). Cela entraîne une dissipation thermique statique, c'est-à-dire une consommation de courant même si le circuit ne commute pas. Une situation similaire se produit dans les circuits CMOS modernes à haute vitesse et haute densité (microprocesseurs, etc.) qui ont également un courant statique significatif, bien que cela soit dû à des fuites et non à la polarisation. Cependant, les circuits CMOS plus anciens et/ou plus lents utilisés dans les ASICs, les SRAM, etc., ont typiquement une très faible consommation statique.

De plus, comme pour les DTL, TTL, ECL, etc., les niveaux logiques d'entrée asymétriques rendent les circuits NMOS et PMOS plus sujets au bruit que les CMOS. Ces inconvénients expliquent pourquoi les CMOS ont maintenant supplanté la plupart de ces types de logique dans les circuits numériques à haute vitesse tels que les microprocesseurs (en dépit du fait que les CMOS étaient initialement très lents par rapport aux portes logiques construites avec des transistors bipolaires).

- Portail de l’électricité et de l’électronique

- Portail des micro et nanotechnologies