Convertisseur analogique-numérique

Un convertisseur analogique-numérique (CAN, parfois convertisseur A/N, ou en anglais ADC pour Analog to Digital Converter ou plus simplement A/D) est un dispositif électronique dont la fonction est de traduire une grandeur analogique en une valeur numérique codée sur plusieurs bits. Le signal converti est généralement une tension électrique.

Pour les articles homonymes, voir Convertisseur, CAN et ADC.

Le résultat de la conversion s'obtient par la formule : où Q est le résultat de Conversion, Ve, la tension à convertir, n le nombre de bits du convertisseur et Vref la tension de référence de la mesure.

Quantification

Le processus de conversion repose sur la quantification d'un signal c'est-à-dire par son appariement au niveau quantifié le plus proche (que l'on pourrait rapprocher du phénomène de l'arrondi pour les nombres à virgule).

La quantification d'un signal en dégrade sa richesse (il y a une perte d'information), c'est donc une transformation destructrice qui s’opère.

On appelle quantum le pas minimum de conversion représenté par la variation du bit de poids faible et qui est aussi la valeur de l’imprécision de mesure. Plus le nombre n de bits du convertisseur sur lesquels s'effectuent la conversion est grand, plus la quantification a un effet réduit dans la dégradation du signal.

Le quantum s'exprime que la fraction élémentaire de la tension de référence (Vref) par la précision de mesure (, où n est le nombre de bits du convertisseur) : .

.png.webp) Signal analogique en temps et amplitude continue |

.png.webp) Signal quantifié à basse résolution |

.png.webp) Signal quantifié à haute résolution |

|---|

Erreur de mesure

La mesure des convertisseurs repose sur la formule :

Il en ressort qu'une variation intempestive de Vref impacte la valeur de Q par la formule : .

Or cette variation de Vref doit introduire une erreur de moins de ½ quantum à pleine échelle ce qui se traduit par : .

Cela signifie que la qualité des tensions de références (et au passage d'alimentations) des convertisseur est un élément fondamental de leur mise en œuvre.

| Nombre de bits | 4 bits | 8 bits | 10 bits | 12 bits | 16 bits | 20 bits | 24 bits | 32 bits |

|---|---|---|---|---|---|---|---|---|

| Tolérance | 3,125% | 2 ‰ | 488 ppm | 122 ppm | 7,6 ppm | 0,47 ppm | 3 ppb | 0,11 ppb |

Technologie des convertisseurs

On dispose pour réaliser les conversions de plusieurs technologies de convertisseurs, chacune ayant des avantages et des inconvénients. Le choix de la technologie repose sur 3 points :

- Sa vitesse de conversion (la fréquence de son horloge ou sa fréquence d'échantillonnage)

- Sa résolution (le nombre de bits)

- Son coût.

Convertisseur à simple rampe

Le convertisseur simple rampe est un objet fictif, ses performances étant trop mauvaise pour permettre son industrialisation. Il existe 2 versions de ces convertisseurs, une analogique et une numérique, toute deux non employée dans l'industrie.

La version analogique est relativement rapide mais très peu précise (en comparaison des autres convertisseurs utilisant des méthodes analogiques comme les convertisseurs à double rampes), là où la version numérique est précise mais lente (là encore en comparaison des autres convertisseurs utilisant des technologies numériques comme les convertisseurs à pesées successives).

Version analogique

On charge à courant constant, proportionnel à Vref, une capacité C en comparant à l'aide d'un comparateur, la tension de la capacité Vcap à la tension à mesurer Ve.

En mesurant la durée de l'impulsion (Tconv), on transforme un rapport de tension en un rapport de temps mesurable à l'aide d'un compteur : .

Ce type de convertisseur nécessite de fréquents recalibrage (en particulier sur la durée nécessaire à charger la capacité jusqu'à Vref) pour pouvoir être fiable, un problème résolu sur les convertisseurs à double rampe.

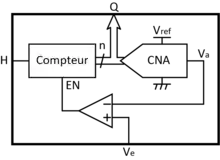

Version numérique

Il est composé d'un compteur n bits, qui tant que l'entrée EN est à 1, compte au rythme de son horloge (H), dont la fréquence est (avec Fe la fréquence d'échantillonnage).

La valeur numérique en sortie du compteur est convertie dans un convertisseur numérique-analogique ou CNA en une tension analogique Va, qui est comparée à Ve.

Lorsque Va devient plus grand que Ve, le comptage s'arrête et la valeur Q sur la sortie est le résultat de la conversion.

Ces convertisseurs ont les mêmes performances en termes de stabilité que les convertisseurs à approximations successives, tout en étant nettement plus lents que ces derniers avec des durées de comptage de , là ou le convertisseur à pesées successives a un temps de conversion .

Convertisseur à double rampe

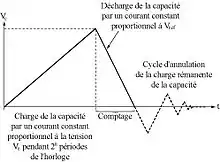

Le convertisseur à double rampe permet des conversions très précises en éliminant les effets de dérive des composants analogiques qu'il utilise, en particulier en annulant l'effet de dérive de la capacité. Son fonctionnement repose sur une comparaison entre une référence et le signal à convertir.

La conversion se déroule en trois étapes :

- on charge une capacité avec un courant proportionnel au signal à convertir pendant un temps fixe (le temps du comptage complet du compteur) ;

- on décharge ensuite la capacité, avec un courant constant issu de la tension de référence, jusqu'à annulation de la tension à ses bornes. Lorsque la tension devient nulle, la valeur du compteur est le résultat de la conversion ;

- on annule enfin la tension aux bornes de la capacité par une série convergente de charges et de décharges (l'objectif étant de décharger totalement la capacité pour ne pas fausser la mesure suivante). On parle en général de phase de relaxation.

Ces convertisseurs sont particulièrement lents (quelques dizaines de millisecondes par cycle, et parfois quelques centaines), et possèdent des résolutions souvent élevées (plus de 16 bits). Ils dérivent peu, dans le temps comme en température.

Technologiquement les Convertisseurs à double rampe ne sont sensibles qu'à la variation de la tension Vref ou a une gigue de la fréquence de l'horloge, ce qui en fait l'un des convertisseur les plus précis existant sur le marché.

Convertisseur Delta-Sigma

.png.webp)

Ce type de convertisseur est basé sur le principe du suréchantillonnage d'un signal d'entrée.

Le principe de fonctionnement d'un convertisseur Delta-Sigma repose sur l'utilisation d'un décimateur dans un système en contre-réaction.

La boucle de contre réaction

- On soustrait à la tension Ve la tension Vc (issue du comparateur) pour produire la tension Va. (DELTA)

- On intègre Va pour produire la tension Vb (Vb = Vb + Va) (SIGMA)

- On compare Vb à 0V pour produire une tension Vc qui vaut soit Vref (1 logique) soit 0V (0 logique)

Prenons l'exemple d'une conversion d'une tension de 3V avec une tension de référence de 5V.

On considère que l'intégrateur est à la base déchargé (Vb = 0V). Or si Vb = 0V alors Vc = 0V.

- Début du premier cycle

- Va = Ve - Vc = 3V

- Vb = 0 + 3V = 3V

- Si Vb = 3V, Vc = Vref = 5V ⇒ Entrée d'un 1 logique dans le décimateur.

- Fin du premier cycle, début du second

- Va = Ve - Vc = 3V - 5V = -2V

- Vb = Vb + Va = 3V - 2V = 1V

- Si Vb = 1V, Vc = Vref = 5V ⇒ Entrée d'un 1 logique dans le décimateur.

- Fin du deuxième cycle, début du troisième

- Va = Ve - Vc = 3V - 5V = -2V

- Vb = Vb + Va = 1V - 2V = -1V

- Si Vb = -1V, Vc = 0V ⇒ Entrée d'un 0 logique dans le décimateur.

- Fin du troisième cycle, début du quatrième

- Va = Ve - Vc = 3V - 0V = 3V

- Vb = Vb + Va = -1V + 3V = 2V

- Si Vb = 2V, Vc = Vref = 5V ⇒ Entrée d'un 1 logique dans le décimateur.

- Fin du quatrième cycle, début du cinquième.

- Va = Ve - Vc = 3V - 5V = -2V

- Vb = Vb + Va = -2V + 2V = 0V

- Si Vb = 0V, Vc = 0V ⇒ Entrée d'un 0 logique dans le décimateur.

- Fin du cinquième cycle, on reboucle au premier cycle.

Le décimateur

Si on regarde les valeurs entrées dans le décimateur, on trouve donc la série 11010110101101011010... à l'infini tant que la tension en entrée Ve ne varie pas.

Pour un convertisseur n bits, on va compter les premiers termes (par exemple pour un convertisseur 4 bits les 16 premières chiffres) le nombre de bits à 1 dans la série (donc si l'on somme tous les échantillons entrées pour les 16 premières valeurs), on trouve pour les 16 premiers bits : 1101011010110101. Soit 1 + 1 + 0 + 1 + 0 + 1 + 1 + 0 + 1 + 0 + 1 + 1 + 0 + 1 + 0 + 1 = 10.

Donc 10 bits à 1 pour 16 bits. Le résultat de la conversion est donc 10 (A en hexadécimal ou 1010 en binaire).

On peut vérifier ce résultat en procédant à l'inverse : ou avec une imprécision de mesure de (2,96875V ≤ Ve ≤ 3,28125V).

Si on applique cette mesure pour un convertisseur 10bits (donc utilisant une série de 2^10 = 1024 mesures) on trouve la valeur 615 (il y a 615 bits à 1 dans la série de 1024 bits) d'où un résultat de mesure : avec une imprécision de mesure de 0,004883V.

Par la suite à chaque période de l'horloge, le convertisseur est capable de fournir une valeur qui va osciller autour de la valeur réelle mesurée. Si on reprend notre convertisseur 4 bits, la première série de mesure était : 1101011010110101, en éliminant le premier échantillon et en entrant le suivant, on trouve 1010110101101011 qui donne à nouveau .

On crée donc un système asservi (la sortie du comparateur est soustraite à l'entrée) qui fait osciller la valeur de l'intégrale du signal à convertir autour d'une valeur de référence (le résultat de la conversion).

Caractéristiques

Le temps de conversion initial est donc long puisqu'il faut périodes pour que le décimateur dispose d'assez d'échantillons pour fournir une somme significative permettant la mesure, mais une fois cette première conversion réalisée, on peut obtenir un résultat à chaque période de l'horloge du décimateur.

De plus si la tension en entrée évolue lentement (moins de 1 quantum par période d'échantillonnage), le convertisseur est capable de suivre le rythme et de fournir à chaque période de l'horloge un résultat de conversion, sans avoir besoin de vider l'intégrateur, ce qui permet de rendre le système d'autant plus réactif que la fréquence d'échantillonnage est grande.

La limite d'évolution du signal Ve dépendant à la fois du nombre de bits (n) et de la tension de référence (Vref) et de la fréquence d'échantillonnage (Fe) sous la forme de . Par exemple pour un convertisseur delta-sigma avec un Vref à 5V, une conversion sur 10 bits et fonctionnant à 1MHz : ΔV ≤ 4,88mV/µs. Et 48,83 mV/µs pour un échantillonnage à 10MHz.

L'intérêt de ce genre de convertisseur réside dans sa grande résolution de sortie possible (16, 24, 32 bits voire plus) pour des signaux d'entrée avec une bande passante modérée.

Ces convertisseurs sont adaptés à la conversion de signaux analogiques issus de capteurs dont la bande passante est souvent faible (par exemple les signaux audio). Les convertisseurs Sigma/Delta sont, par exemple, utilisés dans les lecteurs de CD dans le cas d'une conversion numérique-analogique.

Les technologies Sigma-Delta ont quasi totalement remplacé les technologies à simple ou double rampe.

Les principaux défauts technologiques des Delta-Sigma, en plus de leur grande sensibilité à la valeur de Vref (qui est un problème commun à tous les convertisseurs, mais particulièrement sensible quand le nombre de bits augmente fortement), viennent des hystérésis du comparateur (différence de seuils de basculement entre le passage de 1 à 0 et de 0 à 1) et l'intégrateur (dérive de l'intégration pendant la mesure liées aux courant de fuite des AOP).

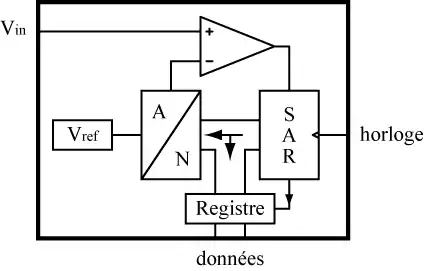

Convertisseur à approximations successives

Très proches en termes de composition des convertisseurs à simple rampe numériques, les convertisseurs à approximations successives (successive-approximation ADC ; aussi appelés convertisseurs à pesées successives) utilisent un processus de dichotomie pour traduire numériquement une tension analogique.

Un séquenceur (généralement nommé SAR pour successive approximation register), couplé à un CNA, produit une tension analogique, qui est comparée au signal à convertir. Le résultat de cette comparaison est alors réintroduit dans le SAR, qui va le prendre en compte, pour la suite du processus de dichotomie, jusqu'à complétion.

Reprenons notre exemple de la conversion avec un convertisseur analogique numérique 4 bits à pesés successives, avec un Vref de 5V, d'une tension analogique de 3V.

Avant d'aller plus loin dans notre exemple, il faut identifier le rôle du CNA, qui génère des tensions allant de 0V pour le code 0000 (0 en base 10) à 4,6875V pour le code 1111 (15 en base 10), qui est la valeur maximale que peut prendre la sortie du CNA. On en tiendra compte dans la suite du calcul en prenant Vref = 4,6875V.

A cause du CNA un convertisseur à pesées successives délivre toujours une valeur par défaut (arrondie à l'entier inférieur).

Analyse pas à pas

- Le SAR positionne son bit de poids fort à 1.

- Le CNA reçoit alors le code binaire 1000 qui se traduit par une tension . Le résultat est comparé à Ve.

- Ve étant plus grand que V, la sortie du comparateur entre un niveau logique 1 dans le SAR.

- Le bit de poids fort est fixé à 1.

- Le SAR positionne le second bit de poids fort à 1.

- Le CNA reçoit alors le code binaire 1100 qui se traduit par une tension . Le résultat est comparé à Ve.

- Ve étant plus petit que V, la sortie du comparateur entre un niveau logique 0 dans le SAR.

- Le bit à 0 remplace le 1 pour le deuxième bit de fort.

- Le SAR positionne le troisième bit de poids fort à 1.

- Le CNA reçoit alors le code binaire 1010 qui se traduit par une tension . Le résultat est comparé à Ve.

- Ve étant plus petit que V, la sortie du comparateur entre un niveau logique 0 dans le SAR.

- Le bit à 0 remplace le 1 pour le troisième bit de fort.

- Le SAR positionne le quatrième bit de poids fort à 1.

- Le CNA reçoit alors le code binaire 1001 qui se traduit par une tension . Le résultat est comparé à Ve.

- Ve étant plus grand que V, la sortie du comparateur entre un niveau logique 1 dans le SAR.

- Le quatrième bit de poids fort est fixé à 1.

Le résultat final est disponible : 1001 en binaire ou 9 (en base 10 ou 16) avec une imprécision de 0,3125V, donc compris entre 2,8125V et 3,125V.

| 1 | 0 | 0 | 0 | 2,5V | 1 | |

|---|---|---|---|---|---|---|

| 1 | 1 | 0 | 0 | 3,75V | 0 | |

| 1 | 0 | 1 | 0 | 3,125V | 0 | |

| 1 | 0 | 0 | 1 | 2,8125V | 1 |

Caractéristiques

Les convertisseurs à approximations successives ont des temps de conversion de l'ordre de la microsecondes, pour des résolutions d'une douzaine de bits environ. Les convertisseurs à pesées successives sont les convertisseurs analogiques numériques les plus rependus, on retrouve généralement un ou plusieurs convertisseurs de ce type dans chaque microcontrôleur.

Outre les effets liés à l'utilisation d'un CNA (et traités précédemment) et la sensibilité à la tension Vref, le convertisseur a pesée successive ne souffre que des effets d'hystérésis du comparateur.

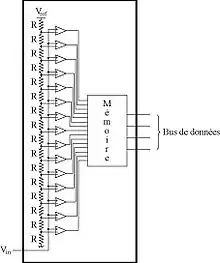

Convertisseur flash

Les convertisseurs FLASH utilisent un réseau de résistances pour produire tensions dans un diviseur de tension, qui seront comparées dans un réseau de comparateurs avec la tension à convertir, puis par utilisation d'une mémoire on traduit le code obtenu en une valeur sur n bits.

Les tensions obtenues aux bornes de chacune des résistances sont ensuite comparées dans comparateurs au signal à convertir.

Un bloc logique combinatoire relié à ces comparateurs donnera le résultat codé sur bits en parallèle.

Cette technique de conversion est très rapide, mais coûteuse en composants et donc utilisée pour les applications critiques comme la vidéo.

Il est difficile d'assurer une bonne linéarité de la conversion, car cela nécessite que toutes les résistances soient égales avec une précision d'autant plus grande qu'il y a un grand nombre de résistances.

Les convertisseurs Flash ont des temps de conversion inférieurs à la microseconde mais une résolution assez faible (de l'ordre de 8 bits) et sont souvent très chers.

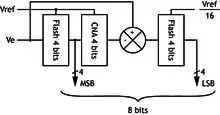

Convertisseurs semi-flash pipeline

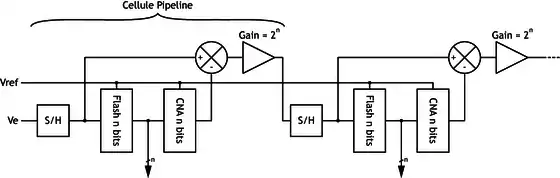

De manière à limiter le nombre total de comparateurs, ces convertisseurs utilisent plusieurs étages flash de précision réduite (typiquement 3 ou 4 bits) chaînés.

Chaque flash pilote un convertisseur numérique-analogique dont la sortie est soustraite au signal analogique d'entrée.

L'étage suivant code le résultat de la différence, améliorant ainsi la précision finale. Un convertisseur semi-flash effectue l'ensemble des opérations en un seul cycle d'horloge, ce qui limite sa vitesse au temps de propagation total le long de la chaîne.

En revanche, un convertisseur pipeline utilise un cycle d'horloge par étage. Ce séquencement nécessite un échantillonneur-bloqueur et un registre par étage mais permet d'être plus rapide puisque plusieurs échantillons sont traités simultanément.

Voir aussi

- Convertisseur numérique-analogique

- Échantillonnage (signal)

- Numérisation

- Quantification (signal)

- Serveur vidéo

- Portail de l’électricité et de l’électronique