Structure de base des registres

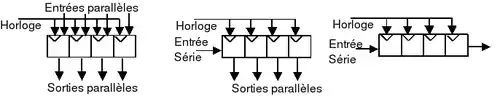

La structure d’un registre dépendra du mode, série ou parallèle, utilisé pour y écrire l'information et pour la lire ensuite.

- écriture et lecture parallèle (registre tampon, Buffer register)

- écriture et lecture en série (Registre à décalage, Shift Register)

- écriture en parallèle et lecture en série (Parallel IN - Serial OUT)

- écriture série et lecture parallèle (Serial IN - parallel OUT)

Quelques exemples sont présentés de manière schématique sur la figure ci-dessus :

- à gauche un registre tampon,

- au centre un serial IN parallel OUT

- à droite un registre à décalage

Le chargement peut être asynchrone ou synchrone.

Un petit essai de spécification d’un registre à décalage par diagramme d'évolution nous montre les limites d'une telle spécification. Pour 4 bits on aura 16 états, ce qui en soi n’est pas énorme. Mais à partir de chaque état on aura beaucoup de transitions (suivant le mode de fonctionnement). Par exemple, un chargement de 4 bits vous emmène sur n’importe quel état (en fonction des données en entrées) et à partir de n’importe quel état.

On aura l’occasion d’utiliser d'autres techniques de spécifications dans la suite.

La logique séquentielle qui ne peut être spécifiée par des diagrammes d'évolution est en général appelée logique séquentielle régulière. La spécification utilise alors des opérateurs arithmétiques comme, par exemple, l’addition pour un compteur.

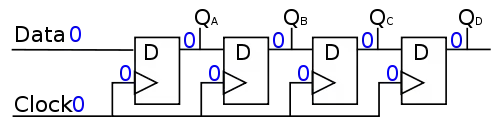

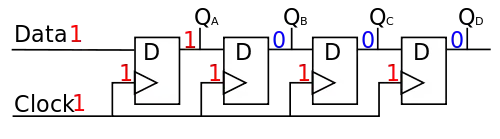

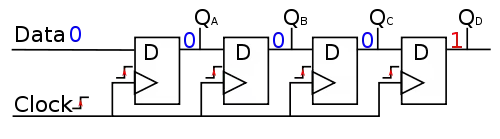

Architecture d’un registre à décalage

Il est relativement simple de réaliser un registre à décalage. Voici comment :

Remarquez la simplicité de l'architecture.

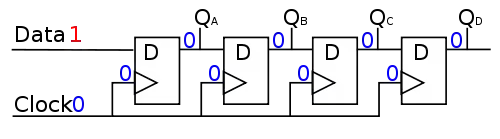

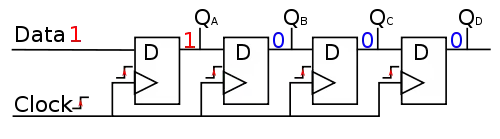

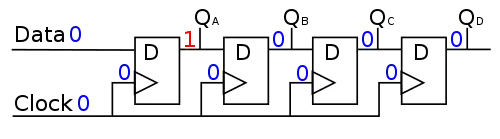

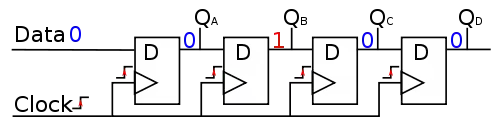

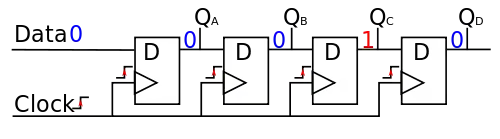

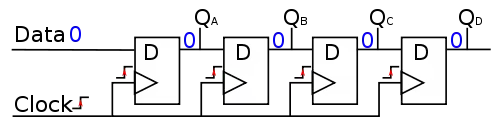

Fonctionnement du registre à décalage

Une série de dessins montre le fonctionnement d’un tel registre :

Le un est maintenant rentré à gauche grâce au front d'horloge.

C'est un zéro qui est rentré et le un précédent se décale lui aussi vers la droite. On continue maintenant en entrant toujours un zéro. Cela aura pour effet de décaler le un jusqu'à sa disparition.

Un registre de 4 bits nécessite 4 fronts d'horloge pour entrer une valeur prédéfinie. Évidemment, l'écriture dans ce registre est synchrone.

Exercices

Exercice 1

Donner un schéma de registre à décalage avec des bascules JK

Exercice 2

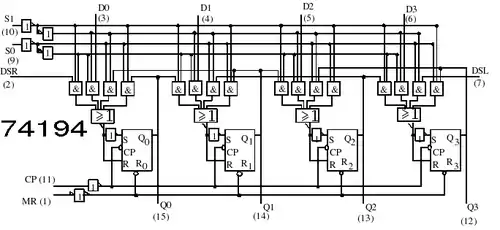

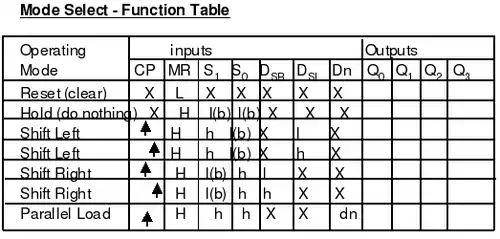

Compléter la table de fonctionnement du 74194 (TTL) à l'aide de son schéma interne.

La figure ci-dessus représente le schéma interne du 74194. Vous y remarquerez plusieurs bizarreries :

- il semble qu’il soit composé de mémoires SR plutôt que de bascules SR, mais un coup d'œil sur la documentation ci-dessous montre qu’il s'agit bien de bascules SR.

- il y a des inverseurs doubles. D'un point de vue logique, ils peuvent être remplacés par des fils.

Si l’on veut connaître parfaitement le fonctionnement de ce registre il nous faut savoir à priori ce que fait la bascule SR quand on lui met S=1 et R=1 (la fameuse priorité). Les habitués auront remarqué l'inverseur sur chacune des entrées des bascules SR ce qui interdit les valeurs identiques simultanées sur R et S !

C'est cette table de fonctionnement qu’il faut compléter dans sa partie droite.

Exercice 3

Donner le schéma d’un registre 3 bits programmable, à écriture et lecture en série par décalage à droite ou à gauche, circulaire ou non. Prévoir deux entrées de programmation P1 et P2, et donner le code de programmation choisi. Utiliser des bascules D synchrones à front montant. Indications : on a encore ici une bonne illustration de la méthode du SI-ALORS. Écrire le programme VHDL correspondant.