VAX

La famille d'ordinateurs VAX-11 (ou simplement VAX) conçue au sein de la société Digital Equipment Corporation (DEC) par Gordon Bell, Bill Demmer, Richie Lary, Steve Rothman et Bill Strecker à partir de 1975 connut un très grand succès. Cette gamme se positionnait comme les successeurs des PDP-11 dont les premiers modèles gardent un mode compatible. D'ailleurs le nom VAX signifie Virtual Address eXtension (Extension de l'adressage virtuel), faisant référence au faible espace d'adressage mémoire disponible sur le PDP-11 (64 ko de base). Les VAX, archétype des machines CISC, sont probablement les ordinateurs qui ont été les plus étudiés dans la littérature informatique. Cette gamme n'est plus fabriquée aujourd'hui.

.jpg.webp)

Architecture

Les VAX reprennent l'architecture du PDP-11 mais la rendent orthogonale en simplifiant le nombre de formats des instructions pour le réduire de 7 à 2, mais pas le nombre d'instructions qui dépasse les 300. Les VAX sont 32 bits et d'architecture little-endian.

Le premier modèle est le VAX-11/780, dont l'étude commence en 1975 et qui sera commercialisé à partir de 1977. C'est une architecture microprogrammée doté d'un pipeline à trois niveaux (fetch, decode, execute).

Les différents modèles sont couramment dénommés 11/730, 11/750, 11/780 etc. Ensuite viendront de nouvelles gammes (6000, 7000, 8000, 9000, 10000). Certains modèles pouvaient être multiprocesseur et/ou dotés d'un processeur vectoriel. Les technologies utilisées : TTL (MSI), puis ECL, et MOS.

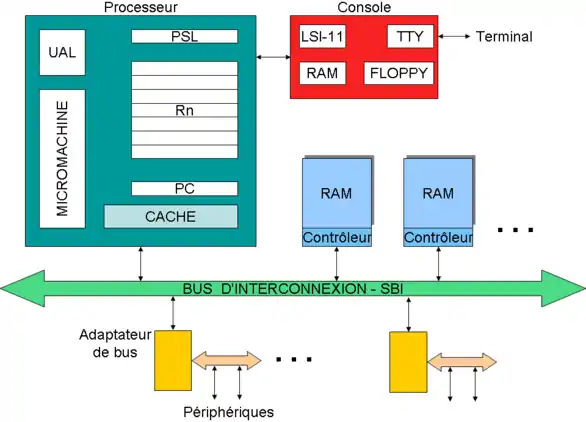

Le modèle 11/780 fourni un bon exemple d'architecture de cette famille. Il est composé de :

- Un processeur ;

- Un bus principal, le SBI - Synchronous Backplane Interconnect ;

- Des contrôleurs mémoire ;

- Des adaptateurs de bus (UNIBUS ou MASSBUS par exemple) ;

- Des périphériques (disques durs, dérouleurs de bandes magnétiques, terminaux, etc.)

- Un sous-système basé sur un LSI-11 pour servir de console.

La gamme des VAX sera ultimement remplacée par des ordinateurs à base du microprocesseur RISC 64 bits « Alpha ».

Bus

Le premier bus du fond de panier employé est appelé SBI pour Synchronous Backplane Interconnect. Il permet de relier le processeur à la mémoire par l'intermédiaire d'un contrôleur. Divers adaptateurs de bus d'entrées/sorties permettent la connexion de différents types de périphériques. Les deux bus principaux utilisés sur le modèle 11/780 sont l'UNIBUS et le MASSBUS. La présence d'un adaptateur UNIBUS n'est pas une surprise pour une machine qui se voulait compatible avec le PDP-11.

Les modèles plus récents définiront de nouveaux bus, surtout destinés à augmenter le débit entre le processeur et la mémoire centrale, par exemple :

Registres

Les VAX possèdent 16 registres de 32 bits, nommés R0 à R15, dont certains ont des fonctions spéciales :

- PC (Program Counter) = R15 : pointeur d'instruction ;

- SP (Stack Pointer) = R14 : pointeur de pile ;

- FP (Frame Pointer) = R13 : pointeur de cadre ;

- AP (Argument Pointer) = R12 : Pointeur de paramètres (R12).

L'état du processeur est stocké dans un registre appelé PSL pour Processor Status Longword.

Types de données

Le nombre de types de données est impressionnant : cela va de la structure la plus simple (un octet) aux plus complexes (des listes chaînées). Néanmoins, le jeu d'instructions étant orthogonal (au moins en ce qui concerne les types entier et flottant), cela n'est pas un problème.

Jeu d'instructions

Les instructions sont codées de façon simple :

- un opcode (un ou deux octets) :

7 0 +---+---+---+---+---+---+---+---+ | code opération | +---+---+---+---+---+---+---+---+

15 8 7 0 +---+---+---+---+---+---+---+---+---+---+---+---+---+---+---+---+ | code opération | FC - FF | +---+---+---+---+---+---+---+---+---+---+---+---+---+---+---+---+

- une suite de spécifications d'opérandes (jusqu'à 6) :

| Code opération |

| Spécification opérande 1 |

| Spécification opérande 2 |

| Spécification opérande 3 |

| … |

| Spécification opérande n |

Par exemple, si l'opérande est un registre, la spécification sera décrite comme ceci :

7 0 +---+---+---+---+---+---+---+---+ | mode | registre | +---+---+---+---+---+---+---+---+

la partie gauche de l'octet spécifie le mode d'adressage (cf. ci-dessous) tandis que la partie droite indique le numéro du registre.

Modes d'adressages

Ils sont décrits dans la table ci-dessous :

| Mode | Symbole | ||

|---|---|---|---|

| Immédiat | #constante | ||

| Registre | Rn | ||

| Registre indirect | (Rn) | Indexé [Rx] | |

| Autodécrément | -(Rn) | ||

| Autoincrément | (Rn)+ | ||

| Autoincrément indirect | @(Rn)+ | ||

| Absolu | @#adresse | ||

| Déplacement | D(Rn) | ||

| Déplacement indirect | @D(Rn) | ||

Rx ne peut être le registre 14.

Exemples

- L'instruction « ADDL3 8(R6), (R7)+, R8 » sera encodée en mémoire comme ceci :

C1 ; ADDL3 A6 ; mode déplacement (compté en) octet(s), registre 6 08 ; valeur du déplacement 87 ; mode indirect post-incrémenté, registre 7 58 ; mode registre direct, registre 8

- L'instruction « INCB (r2)[R3] » :

96 ; INCB 43 ; mode indexé, registre 3 62 ; mode indirect, registre 2

- L'instruction « MOVW #0x200, R3 » :

B0 ; MOVW 8F ; mode immédiat 00 ; bits de poids faible de 0x200 02 ; bits de poids fort de 0x200 53 ; registre 3

Liste des modèles

Ci-dessous la liste des principales machines basées sur les bus UNIBUS, MASSBUS, VAXBI et XMI, étant omises les machines à base du bus QBUS (gamme MicroVAX et VAXstation) :

| modèle | année | techno | tcycle | μcode | cache | bus | perf | pdp |

|---|---|---|---|---|---|---|---|---|

| 11/780 | 1978 | TTL | 200 ns | 6 k × 99 | 8 k | B+U/M | 100 % | o |

| 11/750 | 1980 | TTL | 320 ns | 6 k × 80 | 4 k | B+U/M | 60 % | o |

| 11/730 | 1982 | TTL | 290 ns | 16 k × 24 | n | B+U | 25 % | o |

| 11/782 | 1982 | 11/780 biprocesseur, mémoire partagée | ||||||

| 11/785 | 1984 | TTL | 133 ns | ? | 32 k | B+U/M | 150 % | o |

| 8600 | 1984 | ECL | 80 ns | 8 k × 39 | 16 k | B+U/M | ×4 | o |

| 8650 | 1985 | NMOS | 55 ns | ? | ? | V | ×6 | n |

| 8200 | 1986 | NMOS | 200 ns | 16 × 39 | 8 k | V | 100 % | n |

| 8300 | 1986 | 8200 biprocesseur | ||||||

| 8700 | 1986 | ECL | 45 ns | 16 k × 144 | ? | V | ×6 | n |

| 8800 | 1986 | 8700 biprocesseur | ||||||

| 8500 | 1986 | ? | ? | ? | ? | ? | ×3 | n |

| 8250 | 1987 | ? | 160 ns | ? | ? | V | 120 % | n |

| 6200 | 1988 | CMOS | 80 ns | ? | 256 k | X/V | ×2,8 | n |

| 6300 | 1988 | CMOS | 60 ns | ? | ? | X/V | ×4 | n |

| 6400/400 | 1989 | CMOS | 28 ns (+v) | 1,7 k × 45 | 2 k + 128 k | ? | ×7 | n |

| 9000 | 1989 | ECL | 16 ns (+v) | ? | 128 k | X | ×30-40 | n |

| 4000/300 | 1990 | CMOS | ? | ? | 2 k + 128 k | ? | ×8 | n |

Légende :

Systèmes d'exploitation

Le système mis au point par DEC se nomme VAX-11/VMS pour Virtual Memory System (Système à Mémoire Virtuelle). Il est toujours d'actualité sous le nom OpenVMS. UNIX fut très tôt porté sur cette architecture, d'abord par une version expérimentale de la version 7 d'UNIX, 32/V, puis par BSD et son incarnation par DEC nommée ULTRIX.

Performances

Pendant longtemps on a considéré le VAX-11/780 comme la machine de référence pour définir le MIPS. On s'aperçut un peu plus tard que ce modèle n'exécutait pas 1 million d'instructions par seconde, mais 500 000. On changea donc simplement le nom de l'unité pour le VUP (VAX Unit of Performance) qui vaut 1 pour le modèle 11/780.

Émulation

Notes et références

Voir aussi

Articles connexes

Liens externes

Bibliographie

- VAX Architecture Handbook, Digital, (EB-19580-20) ;

- VAX Hardware Handbook, Digital (EB-21710-20) ;

- Vax Architecture Reference Manual, Richard A. Brunner, Digital Press, (ISBN 1-55558-057-2) ;

- Computer Programming and architecture, the VAX, Henry M. Levy, Richard H. Eckjouse, Jr., Digital Press, (ISBN 1-55558-015-7).

- Portail de l’informatique