Dans ce qui va suivre, nous allons étudier quelques bus relativement connus, autrefois très utilisés dans les ordinateurs. La plupart de ces bus sont très simples : il n'est pas question d'étudier les bus les plus en vogue à l'heure actuelle, du fait de leur complexité. Nous allons surtout étudier les bus série, les bus parallèles étant plus rares.

Le port série RS-232

Pour donner un premier exemple, nous allons aborder le port RS-232, un bus série utilisé sur les ports série qu'on trouvait à l'arrière de nos PC. Celui-ci était autrefois utilisé pour les imprimantes, scanners et autres périphériques du même genre, et est encore utilisé comme interface avec certaines cartes électroniques. Il existe des cartes d'extension permettant d'avoir un port série sur un PC qui n'en a pas, se branchant sur un autre type de port (USB en général).

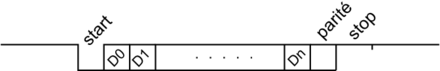

Le bus RS-232 est un bus série asynchrone. Une transmission sur ce bus se résume à l'échange d'un octet de donnée. La trame complète se décompose en un bit de start, l'octet de données à transmettre, un bit de parité, et un bit de stop. Le bit de start est systématiquement un bit qui vaut 0, tandis que le bit de stop vaut systématiquement 1.

L'envoi et la réception des trames sur ce bus se fait simplement en utilisant un composant nommé UART composé de registres à décalages qui envoient ou réceptionnent les données bit par bit sur le bus. Les données envoyer sont placées dans un registre à décalage, dont le bit de sortie est connecté directement sur le bus série. La réception se fait de la même manière : le bus est connecté à l'entrée d'un registre à décalage. Quelques circuits annexes s'occupent du calcul de la parité et de la détection des bits de start et de stop.

Le bus I²c

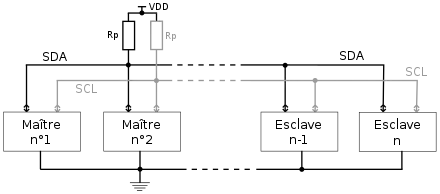

Nous allons maintenant prendre l'exemple typique du bus I2c. Il utilise deux fils pour, respectivement, le transport des données et de l'horloge, nommés SDA (Serial Data Line) et SCL (Serial Clock Line). Chaque composant relié au bus doit avoir deux broches : une pour le fil SDA et une autre pour le fil SCL. Ces deux broches sont des entrées/sorties dites à drain ouvert. Pour rappel, cela veut dire que les broches peuvent mettre le fil à 0 ou le laisser à son état de repos, mais il ne peut pas décider de mettre le fil à 1. Pour obtenir un 1, il faut relier le fil à la tension d'alimentation, ce qui garantit que l'état de repos soit à 1. Cela rend les broches et les circuits plus simples à implémenter.

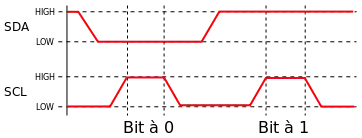

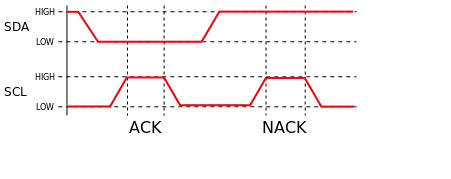

SDA et SCL sont mis à 1 à l'état de repos. L'horloge n'est active que lors du transfert effectif des données, et reste à 1 sinon. Les données sont transmises bit par bit, avec pour détail que les données sont maintenues tant que l’horloge est à 1. Dit autrement, le signal de donnée ne montre aucun front entre deux fronts de l'horloge. Retenez bien cette remarque, car elle n'est valide que pour la transmission d'un bit de données (et les bits d'ACK/NACK).

|

|

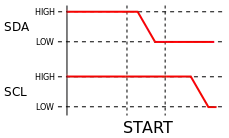

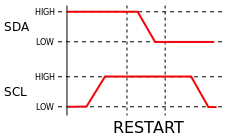

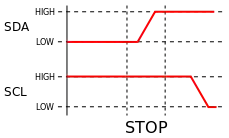

Un transfert de données commence avec un bit START, qui est codé par une mise à 0 de l'horloge avant le fil de donnée, et se termine avec un bit STOP, qui correspond aux conditions inverses. Les deux correspondent à une violation de la règle qui veut qu'il y ait absence de front sur le signal de données entre deux fronts d'horloge.

|

|

|

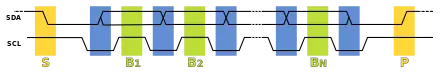

Pour résumer, une transmission I²c est schématisée ci-dessous. Sur ce schéma, S représente le marqueur de début de transmission (start), puis chaque période en bleue est celle ou la ligne de donnée peut changer d'état pour le prochain bit de données à transmettre durant la période verte qui suit notée B1, B2... jusqu'à la période final notée P marquant la fin de transmission (stop).