Mémoire. Ce mot signifie dans le langage courant le fait de se rappeler quelque chose, de pouvoir s'en souvenir. La mémoire d'un ordinateur fait exactement la même chose (le nom de mémoire n'a pas été donné par hasard) mais dans notre ordinateur. Son rôle est de retenir des données stockées sous la forme de suites de bits, afin qu'on puisse les récupérer si nécessaire et les traiter.

Les mémoires volatiles et non-volatiles

Lorsque vous éteignez votre ordinateur, le système d'exploitation et les programmes que vous avez installés ne s'effacent pas, contrairement au document Word que vous avez oublié de sauvegarder. Les programmes et le système d'exploitation sont placés sur une mémoire qui ne s'efface pas quand on coupe le courant, contrairement à votre document Word non-sauvegardé. Cette observation nous permet de classer les mémoires en deux types : les mémoires non-volatiles conservent leurs informations quand on coupe le courant, alors que les mémoires volatiles les perdent.

Les mémoires volatiles peuvent être divisées en deux catégories : les mémoires statiques et mémoires dynamiques. Les données d'une mémoire statique ne s'effacent pas tant qu'elles sont alimentées en courant. Avec les mémoires dynamiques, les données s'effacent en quelques millièmes ou centièmes de secondes si l'on n'y touche pas. Il faut donc réécrire chaque bit de la mémoire régulièrement, ou après chaque lecture, pour éviter qu'il ne s'efface : on doit effectuer régulièrement un rafraîchissement mémoire. Le rafraîchissement prend du temps, et a tendance à légèrement diminuer la rapidité des mémoires dynamiques.

Les mémoires ROM et RWM

Une autre différence concerne la façon dont on peut accéder aux informations stockées dans la mémoire. Celle-ci permet de faire la différence entre les mémoires ROM et les mémoires RWM.

Les mémoires ROM

Avec les mémoires ROM, on peut récupérer les informations dans la mémoire, mais pas les modifier : la mémoire est dite accessible en lecture. Ces mémoires sont toutes des mémoires non-volatiles, mais la réciproque n'est pas vraie (la confusion est commune). Si on ne peut pas écrire dans une ROM, certaines permettent cependant de réécrire intégralement leur contenu : on dit qu'on reprogramme la ROM. Insistons sur la différence entre reprogrammation et écriture : l'écriture permet de modifier un byte sélectionné/adressé, alors que la reprogrammation efface toute la mémoire et la réécrit en totalité. De plus, la reprogrammation est généralement beaucoup plus lente qu'une écriture, sans compter qu'il est plus fréquent d'écrire dans une mémoire que la reprogrammer. Ce terme de programmation vient du fait que les mémoires ROM sont souvent utilisées pour stocker des programmes sur certains ordinateurs assez simples.

On peut classer les mémoires ROM en plusieurs types :

- les mask ROM sont fournies déjà programmées et ne peuvent pas être reprogrammées ;

- les mémoires PROM sont fournies intégralement vierges, et on peut les programmer une seule fois ;

- les mémoires RPROM sont reprogrammables, ce qui signifie qu'on peut les effacer pour les programmer plusieurs fois ;

- les mémoires EPROM s'effacent avec des rayons UV et peuvent être reprogrammées plusieurs fois de suite ;

- certaines RPROM peuvent être effacées par des moyens électriques : ce sont les mémoires EEPROM.

Les mémoires de type mask ROM sont utilisées dans quelques applications particulières. Par exemple, elles étaient utilisées sur les vieilles consoles de jeux, pour stocker le jeu vidéo dans les cartouches. Elles servent aussi pour les firmware divers et variés, comme le firmware d'une imprimante ou d'une clé USB. Par contre, le BIOS d'un PC (qui est techniquement un firmware) est stocké dans une mémoire EEPROM, ce qui explique qu'on peut le mettre à jour (on dit qu'on flashe le BIOS).

Les mémoires RWM

Sur les mémoires RWM, on peut récupérer les informations dans la mémoire et les modifier : la mémoire est dite accessible en lecture et en écriture. Quand un composant souhaite échanger des données avec une mémoire RWM, il doit préciser le sens de transfert : lecture ou écriture. Pour préciser ce sens de transfert à la mémoire, il va devoir utiliser un bit du bus de commande nommé READ/WRITE, ou encore R/W (read veut dire lecture en anglais, alors que write veut dire écriture). Il est souvent admis par convention que R/W à 1 correspond à une lecture, tandis que R/W vaut 0 pour les écritures. Ce bit de commande est évidemment inutile sur les mémoires ROM, vu qu'elles ne peuvent effectuer que des lectures. Les mémoires RWM peuvent être aussi bien volatiles que non-volatiles.

Attention aux abus de langage : le terme mémoire RWM est souvent confondu dans le langage commun avec les mémoires RAM.

L'adressage et les accès mémoire

Les mémoires se différencient aussi par la méthode d'accès aux données mémorisées.

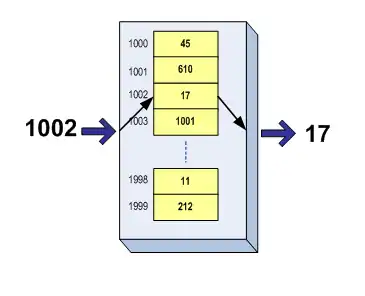

Les mémoires adressables

Les mémoires actuelles utilisent l'adressage : chaque case mémoire se voit attribuer un numéro, l'adresse, qui va permettre de la sélectionner et de l'identifier parmi toutes les autres. On peut comparer une adresse à un numéro de téléphone (ou à une adresse d'appartement) : chacun de vos correspondants a un numéro de téléphone et vous savez que pour appeler telle personne, vous devez composer tel numéro. Les adresses mémoires en sont l'équivalent pour les cases mémoires. Ces mémoires adressables peuvent se classer en deux types : les mémoires à accès aléatoire, et les mémoires adressables par contenu.

Les mémoires à accès aléatoire sont des mémoires adressables, sur lesquelles on doit préciser l'adresse de la donnée à lire ou modifier. Certaines d'entre elles sont des mémoires électroniques non-volatiles de type ROM : on les nomme, par abus de langage, des mémoires ROM. D'autres sont des mémoires volatiles RWM : elles portent alors, par abus de langage, le nom de mémoires RAM (Random Access Memory). Parmi les mémoires RAM volatiles, on peut distinguer les SRAM des DRAM : les premières sont des mémoires statiques alors que les secondes sont des mémoires dynamiques.

Les mémoires associatives fonctionnent comme une mémoire à accès aléatoire, mais dans le sens inverse. Au lieu d'envoyer l'adresse pour accéder à la donnée, on va envoyer la donnée pour récupérer son adresse : à la réception de la donnée, la mémoire va déterminer quelle case mémoire contient cette donnée et renverra l'adresse de cette case mémoire. Cela peut paraitre bizarre, mais ces mémoires sont assez utiles dans certains cas de haute volée. Dès que l'on a besoin de rechercher rapidement des informations dans un ensemble de données, ou de savoir si une donnée est présente dans un ensemble, ces mémoires sont reines. Certains circuits internes au processeur ont besoin de mémoires qui fonctionnent sur ce principe. Mais laissons cela à plus tard.

Les mémoires caches

Sur les mémoires caches, chaque donnée se voit attribuer un identifiant, qu'on appelle le tag. Une mémoire à correspondance stocke non seulement la donnée, mais aussi l'identifiant qui lui est attribué : cela permet ainsi de mettre à jour l'identifiant, de le modifier, etc. En somme, le Tag remplace l'adresse, tout en étant plus souple. La mémoire cache stocke donc des couples tag-donnée. A chaque accès mémoire, on envoie le tag de la donnée voulue pour sélectionner la donnée.

Il faut noter qu'il est possible de créer une mémoire cache en utilisant une mémoire RAM et une mémoire associative, ainsi que quelques circuits pour faire le lien entre les deux.

Les mémoires séquentielles

Sur d'anciennes mémoires, comme les bandes magnétiques, on était obligé d'accéder aux données dans un ordre prédéfini. On parcourait la mémoire dans l'ordre, en commençant par la première donnée : c'est l'accès séquentiel. Pour lire ou écrire une donnée, il fallait visiter toutes les cases mémoires précédentes avant de tomber sur la donnée recherchée. Et impossible de revenir en arrière ! Il existe plusieurs types de mémoires séquentielles, qui se différencient par l'ordre dans lequel les données sont lues ou écrites. Pour les mémoires électroniques, on distingue ainsi les registres à décalage des mémoires LIFO et FIFO. Cependant, certaines mémoires magnétiques ou optiques sont des mémoires séquentielles. Pensez notamment aux CD-ROM et aux DVD/Blue-Ray qui peuvent être vu comme des mémoires séquentielles, dans une certaine mesure.

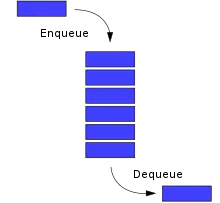

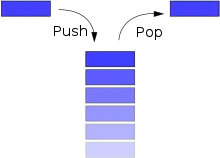

Les registres à décalage ne sont pas les seules à imposer un ordre d'accès aux données. Il existe deux autres types de mémoires qui forcent l'ordre d'accès : les mémoires FIFO et LIFO. Dans les deux cas, les données sont triées dans la mémoire dans l'ordre d'écriture, ce dernier étant la même chose que l'ordre d'arrivée. La différence est qu'une lecture dans une mémoire FIFO renvoie la donnée la plus ancienne, alors que pour une mémoire LIFO, elle renverra la donnée la plus récente, celle ajoutée en dernier dans la mémoire. Dans les deux cas, la lecture sera destructrice : la donnée lue est effacée.

On peut voir les mémoires FIFO comme des files d'attente, des mémoires qui permettent de mettre en attente des données tant qu'un composant n'est pas prêt. Seules deux opérations sont possibles sur de telles mémoires : mettre en attente une donnée (enqueue, en anglais) et lire la donnée la plus ancienne (dequeue, en anglais).

De même, on peut voir les mémoires LIFO comme des piles de données : toute écriture empilera une donnée au sommet de cette mémoire LIFO (on dit qu'on push la donnée), alors qu'une lecture enlèvera la donnée au sommet de la pile (on dit qu'on pop la donnée).

l'interface avec le bus

Une mémoire communique avec d'autres composants : le processeur, les entrées-sorties, et peut-être d'autres. Pour cela, la mémoire est reliée à un ou plusieurs bus. Suivant la mémoire et sa place dans la hiérarchie mémoire, le bus sera plus ou moins spécialisé. Par exemple, la mémoire principale est reliée au processeur et aux entrées-sorties via le bus système. Pour les autres mémoires, la logique est la même, si ce n'est que la mémoire est reliée à d'autres composants électroniques : une unité de calcul pour les registres, par exemple.

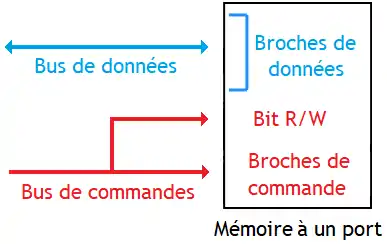

Dans tous les cas, le bus connecté à la mémoire est composé de deux ensembles de fils : le bus de données et le bus de commande. Le bus de données permet les transferts de données avec la mémoire, alors que le bus de commande prend en charge tout le reste. Nous allons commencer par voir le bus de données avant le bus de commandes, vu que son abord est plus simple.

Le bus de données

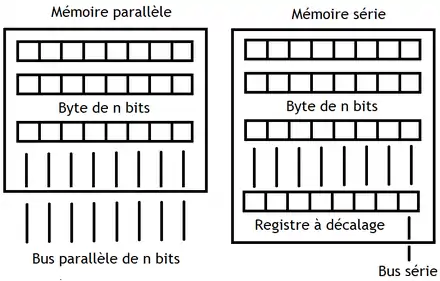

Le bus de données est généralement un bus bidirectionnel (pour les lectures et écritures), rarement unidirectionnel (pour les mask ROM qui ne gèrent que la lecture). Le bus de données transmet un nombre fixe de bits, qui est le plus souvent égal à la taille d'un byte. Si c'est le cas, le bus de données peut transmettre un byte à chaque transmission (à chaque cycle d'horloge). Une mémoire et/ou un bus qui permet ce genre de choses est appelé une mémoire ou un bus parallèle. Quelques mémoires sont cependant connectées à un bus qui ne peut transmettre qu'un seul bit à la fois. Un tel bus est appelé un bus série, la mémoire étant appelée une mémoire série. Ces mémoires permettent de lire ou écrire par bytes complets, qui sont transmis bits par bits sur le bus de données. La conversion entre byte et flux de bits sur le bus est réalisée par un simple registre à décalage. On pourrait croire que de telles mémoires séries sont rares, mais ce n'est pas le cas. Les mémoires Flash, très utilisées dans les clés USB ou les disques durs SSD sont des mémoires séries.

Le bus de commande et d'adresse

Le bus de commande transmet des bits qui ont une fonction fixée lors de la conception de la mémoire. Le bus de commande dépend énormément du bus utilisé ou de la mémoire. Certains bus de commande se contentent d'un seul bit, d'autres en ont une dizaine, et d'autres en ont une petite centaine. Comme on le verra plus bas, certaines mémoires adressables ont des broches dédiées aux adresses, qui sont connectées au bus d'adresse. Mais certaines arrivent cependant à s'en passer. Pour résumer, le bus d'adresse est facultatif, seules certaines mémoires en ayant réellement un. Dans ce qui va suivre, nous allons parler à la fois du bus de commandes et du bus d'adresse. On peut d'ailleurs voir le bus d'adresse comme une sous-partie du bus de commandes, raison pour laquelle nous voyons les deux en même temps.

Les bits Chip Select et Output Enable

La majorité des mémoires possède deux broches/bits qui servent à l'activer ou la désactiver : le bit CS (Chip Select). Lorsque ce bit est à 1, toutes les autres broches sont désactivées, qu'elles appartiennent au bus de données ou de commande. On verra dans quelques chapitres l'utilité de ce bit. Pour le moment, on peut dire qu'il permet d'éteindre une mémoire (temporairement) inutilisée. L'économie d'énergie qui en découle est souvent intéressante.

Tout aussi fréquent, le bit OE (Output Enable) désactive les broches du bus de données, laissant cependant le bus de commande fonctionner. Ce bit déconnecte la mémoire du bus de données, stoppant les transferts. Il a une utilité similaire au bit CE, avec cependant quelques différences. Ce bit ne va pas éteindre la mémoire, mais juste stopper les transmissions. L'économie d'énergie est donc plus faible. Cependant, déconnecter la mémoire est beaucoup plus rapide que de l'éteindre. On verra dans quelques chapitres l'utilité de ce bit. Grossièrement, il permet de déconnecter une mémoire quand un composant prioritaire souhaite communiquer sur le bus, en même temps que la mémoire.

L'entrée d'horloge ou de synchronisation

Certaines mémoires assez anciennes n'étaient pas synchronisées par un signal d'horloge, mais par d'autres procédés : on les appelle des mémoires asynchrones. Les bus de commande de ces mémoires devaient transmettre les informations de synchronisation, sous la forme de bits de synchronisation.

D'autres mémoires sont cadencées par un signal d'horloge : elles portent le nom de mémoires synchrones. Ces mémoires ont un bus de commande beaucoup plus simple, qui n'a qu'une seule broche de synchronisation. Celle-ci reçoit le signal d'horloge, d'où le nom d'entrée d'horloge qui lui est donné.

Le bit R/W du bus de commande

Sur la plupart des mémoires, le bus de données sert aussi bien pour les lectures que pour les écritures. Dans une telle situation, le bus de commande doit préciser à la mémoire s'il faut effectuer une lecture ou une écriture. Pour cela, le bus envoie sur le bus de commande un bit appelé bit R/W, qui indique s'il faut faire une lecture ou une écriture. Il vaut 1 pour une lecture et 0 pour une écriture.

Sur d'autres mémoires, on trouve deux bus : un dédié aux lectures et un autre pour les écritures. Pas besoin de bit R/W sur ces mémoires (en théorie, du moins). Ces mémoires ont un avantage : elles permettent d'effectuer une lecture en même temps qu'une écriture. Cependant, cet avantage signifie que la conception interne de la mémoire est naturellement plus compliquée. Par exemple, la mémoire doit gérer le cas où la donnée lue est identique à celle écrite en même temps. Cela arrive notamment sur les mémoires adressables, plus rarement sur les autres mémoires. L'augmentation du nombre de broches est aussi un désavantage.

.png.webp)

Le bus d'adresse et le bit ALE

Toutes les mémoires adressables sont naturellement connectées au bus. Mais celui-ci ne se limite plus à un bus de données couplé à un bus de commande : il faut ajouter un troisième bus pour envoyer les adresses à la mémoire (ou les récupérer, sur une mémoire associative). Ce dernier est appelé le bus d'adresse.

Il existe une petite astuce pour économiser des fils : utiliser un bus qui servira alternativement de bus de donnée ou d'adresse. Ces bus rajoutent un bit sur le bus de commande, qui précise si le contenu du bus est une adresse ou une donnée. Ce bit Adresse Line Enable, aussi appelé bit ALE, vaut 1 quand une adresse transite sur le bus, et 0 si le bus contient une donnée (ou l'inverse !). Ce genre de bus est plus lent pour les écritures : l'adresse et la donnée à écrire ne peuvent pas être envoyées en même temps. Par contre, les lectures ne posent pas de problèmes, vu que l'envoi de l'adresse et la lecture proprement dite ne sont pas simultanées. Heureusement, les lectures en mémoire sont bien plus courantes que les écritures, ce qui fait que la perte de performance due à l'utilisation d'un bus multiplexé est souvent supportable.

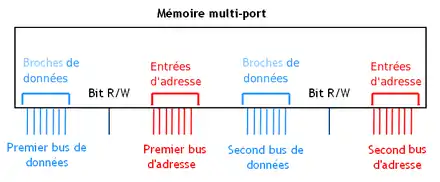

Les mémoires multiports

Les mémoires multiports sont reliées non pas à un, mais à plusieurs bus. Chaque bus est connecté sur la mémoire sur ce qu'on appelle un port. Ces mémoires permettent de transférer plusieurs données à la fois, une par port. Le débit est sont donc supérieur à celui des mémoires mono-port. De plus, chaque port peut être relié à des composants différents, ce qui permet de partager une mémoire entre plusieurs composants. Comme exemple de mémoire multiports, on a vu plus haut que certaines mémoires ont un bus sur lequel on ne peut que lire une donnée, et un autre sur lequel on ne peut qu'écrire.