Les mémoires actuelles sont un plus complexes que les mémoires vues dans les chapitres précédents. Ce chapitre va vous expliquer dans les grandes lignes en quoi nos mémoires actuelles se démarquent des autres. On verra que les mémoires modernes ne sont que des améliorations des mémoires vues précédemment.

Les mémoires SDRAM

Les mémoires asynchrones ont laissé la place aux mémoires SDRAM, qui sont synchronisées avec le bus par une horloge. L'utilisation d'une horloge a comme avantage des temps d'accès fixes : le processeur sait qu'un accès mémoire prendra un nombre déterminé de cycles d'horloge et peut faire ce qu'il veut dans son coin durant ce temps. Avec les mémoires asynchrones, le processeur ne pouvait pas prévoir quand la donnée serait disponible et ne faisait rien tant que la mémoire n'avait pas répondu : il exécutait ce qu'on appelle des wait states en attendant que la mémoire ait fini.

Le mode rafale

Sur les SDRAM, les paramètres qui ont trait au mode rafale sont modifiables, programmables. Le contrôleur mémoire interne de la SDRAM mémorise ces informations dans un registre de 10 bits, le registre de mode. Il contient un bit qui permet de préciser s'il faut effectuer des accès normaux ou des accès en rafale. Il mémorise aussi le nombre d'octets consécutifs à lire ou écrire. On peut ainsi accéder à 1, 2, 4, ou 8 octets en une seule fois, alors que les EDO ne permettaient que des accès à 4 octets consécutifs.

Qui plus est, il existe deux types d'accès en rafale sur les SDRAM : l'accès entrelacé, et l'accès séquentiel. Le mode séquentiel est le mode rafale normal : on accède à des octets consécutifs les uns après les autres. Le mode entrelacé utilise un ordre différent. Avec ce mode de rafale, le contrôleur mémoire effectue un XOR bit à bit entre un compteur (incrémenté à chaque accès) et l'adresse de départ pour calculer la prochaine adresse de la rafale.

Un accès en rafale parcourt un mot (un bloc de mots mémoires de même taille que le bus). Un accès en rafale ne commence pas forcément au début du mot, mais peut commencer à n'importe quel mot mémoire dans le mot. Dans ce cas, la rafale reprend au premier mot mémoire une fois arrivé au bout d'un mot. Par exemple, regardons ce qui se passe lors de différents accès. Dans ce qui va suivre, on va noter les cases mémoires appartenant à un de ces blocs 1, 2, 3, 4, 5, 6, 7, 8 et 9. Un accès en mode Burst n'est pas obligé de commencer par lire ou écrire le bloc 1 : on peut très bien commencer par lire ou écrire au bloc 3, par exemple. Si l'on veut effectuer un accès en Burst sur 8 cases mémoires, on commence par accéder à la case mémoire numérotée 3, puis la 4, la 5, la 6 et la 7. Puis, l'accès reprend au bloc 1 et on accède aux blocs 1, 2 et 3. En clair, une fois arrivé au bout d'un bloc de 8 cases mémoires, on reprend au début.

Les commandes SDRAM

Le bus de commandes d'une SDRAM contient évidemment un signal d'horloge, pour cadencer la mémoire, mais pas que. En tout, 18 fils permettent d'envoyer des commandes à la mémoire, commandes qui vont effectuer une lecture, une écriture, ou autre chose dans le genre. Les commandes en question sont des demandes de lecture, d'écriture, de préchargement et autres. Elles sont codées par une valeur bien précise qui est envoyée sur les 18 fils du bus de commande. Ces commandes sont nommées READ, READA, WRITE, WRITEA, PRECHARGE, ACT, ...

| Bit CS | Bit RAS | Bit CAS | Bit WE | Bits de sélection de banque (2 bits) | Bit du bas d'adresse A10 | Reste du bus d'adresse | Nom de la commande : Description |

|---|---|---|---|---|---|---|---|

| 1 | X | Absence de commandes. | |||||

| 0 | 1 | 1 | 1 | X | No Operation : Pas d'opération | ||

| 0 | 1 | 1 | 0 | X | Burst Terminante : Arrêt d'un accès en rafale en cours. | ||

| 0 | 1 | 0 | 1 | Adresse de la banque | 0 | Adresse de la colonne | READ : lire une donnée depuis la ligne active. |

| 0 | 1 | 0 | 1 | Adresse de la banque | 1 | Adresse de la colonne | READA : lire une donnée depuis la ligne active, avec rafraichissement automatique de la ligne. |

| 0 | 1 | 0 | 0 | Adresse de la banque | 0 | Adresse de la colonne | WRITE : écrire une donnée depuis la ligne active. |

| 0 | 1 | 0 | 0 | Adresse de la banque | 1 | Adresse de la colonne | WRITEA : écrire une donnée depuis la ligne active, avec rafraichissement automatique de la ligne. |

| 0 | 0 | 1 | 1 | Adresse de la banque | Adresse de la ligne | ACT : charge une ligne dans le row buffer. | |

| 0 | 0 | 1 | 0 | Adresse de la banque | 0 | X | PRECHARGE : précharge le row buffer dans la banque voulue. |

| 0 | 0 | 1 | 0 | Adresse de la X | 1 | X | PRECHARGE ALL : précharge le row buffer dans toutes les banques. |

| 0 | 0 | 0 | 1 | X | Auto refresh : Demande de rafraichissement, gérée par la SDRAM. | ||

| 0 | 0 | 0 | 0 | 00 | Nouveau contenu du registre de mode | LOAD MODE REGISTER : configure le registre de mode. | |

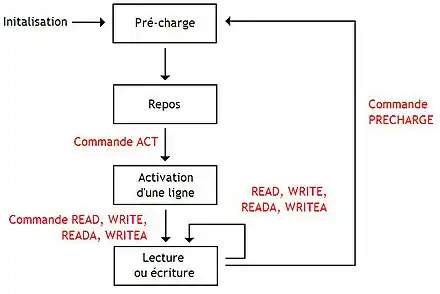

Les commandes READ et WRITE ne peuvent se faire qu'une fois que la banque a été activée par une commande ACT. Une fois la banque activée par une commande ACT, il est possible d'envoyer plusieurs commandes READ ou WRITE successives. Ces lectures ou écritures accèderont à la même ligne, mais à des colonnes différentes. Le commandes ACT se font à partir de l'état de repos, l'état où toutes les banques sont préchargées. Par contre, les commandes MODE REGISTER SET et AUTO REFRESH ne peuvent se faire que si toutes les banques sont désactivées.

Le fonctionnement simplifié d'une SDRAM peut se résumer dans ce diagramme :

Les délais mémoires

Il faut un certain temps pour sélectionner une ligne ou une colonne, sans compter qu'une SDRAM doit gérer d'autres temps d'attente plus ou moins bien connus : ces temps d'attente sont appelés des délais mémoires. La façon de mesurer ces délais varie : sur les mémoires FPM et EDO, on les mesure en unités de temps (secondes, millisecondes, micro-secondes, etc.), tandis qu'on les mesure en cycles d'horloge sur les mémoires SDRAM.

| Timing | Description |

|---|---|

| tRAS | Temps mis pour sélectionner une ligne. |

| tCAS | Temps mis pour sélectionner une colonne. |

| tRP | Temps mis pour réinitialiser le row buffer et décharger la ligne. |

| tRCD | Temps entre la fin de la sélection d'une ligne, et le moment où l'on peut commencer à sélectionner la colonne. |

| tWTR | Temps entre une lecture et une écriture consécutives. |

| tCAS-to-CAS | Temps minimum entre deux sélections de deux colonnes différentes. |

Ces timings influencent grandement la vitesse à laquelle on accède à une donnée dans la mémoire. Et oui, car suivant la disposition des données dans la mémoire, l'accès peut être plus ou moins rapide. Il existe ainsi quelques possibilités plus ou moins différentes, qu'on va vous citer.

- Premier cas : la donnée que l'on cherche à lire est présente sur la même ligne que la donnée qui a été accédée avant elle. Cela se produit souvent lorsque l'on doit accéder à des données proches les unes des autres en mémoire. Dans ce cas, la ligne entière a été recopiée dans le Row Buffer et on n'a pas à la sélectionner : on doit juste changer de colonne. Ce genre de situation s'appelle un Row Buffer Hit. Le temps nécessaire pour accéder à notre donnée est donc égal au temps nécessaire pour sélectionner une colonne (le tCAS auquel il faut ajouter le temps nécessaire entre deux sélections de deux colonnes différentes (le t-CAS-To-CAS).

- Second cas : on accède à une donnée située dans une ligne différente : c'est un Row Buffer Miss. Et là, c'est une catastrophe ! Dans ce genre de cas, il faut en effet vider le Row Buffer, qui contient la ligne précédente, en plus de sélectionner la ligne et la colonne. On doit donc ajouter le tRP au tRAS et au tCAS pour avoir le temps d'accès total à notre donnée.

Les délais/timings mémoire ne sont pas les mêmes suivant la barrette de mémoire que vous achetez. Certaines mémoires sont ainsi conçues pour avoir des timings assez bas et sont donc plus rapides, et surtout : beaucoup plus chères que les autres. Le gain en performances dépend beaucoup du processeur utilisé et est assez minime comparé au prix de ces barrettes. Les circuits de notre ordinateur chargés de communiquer avec la mémoire (ceux placés soit sur la carte mère, soit dans le processeur), doivent connaitre ces timings et ne pas se tromper : sans ça, l’ordinateur ne fonctionne pas.

Les SDRAM standards

Les mémoires SDRAM sont standardisées par un organisme international, le JEDEC, et ont été déclinées en versions de performances différentes. Les voici :

| Nom standard | Fréquence | Bande passante |

|---|---|---|

| PC66 | 66 mhz | 528 Mio/s |

| PC66 | 100 mhz | 800 Mio/s |

| PC66 | 133 mhz | 1064 Mio/s |

| PC66 | 150 mhz | 1200 Mio/s |

Les mémoires DDR

Les mémoires SDRAM récentes sont des mémoires de type dual data rate, voire quad data rate (voir le chapitre précédent pour ceux qui ont oublié) : elles portent ainsi le nom de mémoires DDR. Plus précisément, le plan mémoire des DDR est deux fois plus large que le bus mémoire, même si les deux sont commandés par un même signal d'horloge : là où les transferts avec le plan mémoire ont lieu sur front montant, les transferts de données sur le bus ont lieu sur les fronts montants et descendants de l'horloge. Il y a donc deux transferts de données sur le bus pour chaque cycle d'horloge, ce qui permet de doubler le débit sans toucher à la fréquence. D'autres différences mineures existent entre les SDRAM et les mémoires DDR. Par exemple, la tension d'alimentation des mémoires DDR est plus faible que pour les SDRAM.

Les types de mémoires DDR

Les mémoires DDR sont standardisées par un organisme international, le JEDEC, et ont été déclinées en versions DDR1, DDR2, DDR3, et DDR4. Il existe enfin d'autres types de mémoires DDR, non-standardisées par le JEDEC : les mémoires GDDR, pour graphics double data rate, utilisées presque exclusivement sur les cartes graphiques. Il en existe plusieurs types pendant que j'écris ce tutoriel : GDDR, GDDR2, GDDR3, GDDR4, et GDDR5. Mais attention, il y a des différences avec les DDR normales : les GDDR sont des mémoires multiports et elles ont une fréquence plus élevée que les DDR normales, avec des temps d'accès plus élevés (sauf pour le tCAS).

Il existe quatre types de mémoires DDR1 officialisés par le JEDEC.

| Nom standard | Nom des modules | Fréquence du bus | Débit | Tension d'alimentation |

|---|---|---|---|---|

| DDR 200 | PC-1600 | 100 Mhz | 1,6 gibioctets seconde | 2,5 Volts |

| DDR 266 | PC-2100 | 133 Mhz | 2,1 gibioctets seconde | 2,5 Volts |

| DDR 333 | PC-2700 | 166 Mhz | 2,7 gibioctets seconde | 2,5 Volts |

| DDR 400 | PC-3200 | 200 Mhz | 3,2 gibioctets seconde | 2,6 Volts |

Avec les mémoires DDR2, 5 types de mémoires sont officialisées par le JEDEC. Diverses améliorations ont été apportées sur les mémoires DDR2 : la tension d'alimentation est notamment passée de 2,5/2,6 Volts à 1,8 Volts.

| Nom standard | Nom des modules | Fréquence du bus | Débit |

|---|---|---|---|

| DDR2 400 | PC2-3200 | 100 Mhz | 3,2 gibioctets par seconde |

| DDR2 533 | PC2-4200 | 133 Mhz | 4,2 gibioctets par seconde |

| DDR2 667 | PC2-5300 | 166 Mhz | 5,3 gibioctets par seconde |

| DDR2 800 | PC2-6400 | 200 Mhz | 6,4 gibioctets par seconde |

| DDR2 1066 | PC2-8500 | 266 Mhz | 8,5 gibioctets par seconde |

Avec les mémoires DDR3, 6 types de mémoires sont officialisées par le JEDEC. Diverses améliorations ont été apportées sur les mémoires DDR3 : la tension d'alimentation est notamment passée à 1,5 Volts.

| Nom standard | Nom des modules | Fréquence du bus | Débit |

|---|---|---|---|

| DDR3 800 | PC3-6400 | 100 Mhz | 6,4 gibioctets par seconde |

| DDR3 1066 | PC3-8500 | 133 Mhz | 8,5 gibioctets par seconde |

| DDR3 1333 | PC3-10600 | 166 Mhz | 10,6 gibioctets par seconde |

| DDR3 1600 | PC3-12800 | 200 Mhz | 12,8 gibioctets par seconde |

| DDR3 1866 | PC3-14900 | 233 Mhz | 14,9 gibioctets par seconde |

| DDR3 2133 | PC3-17000 | 266 Mhz | 17 gibioctets par seconde |