Dans ce chapitre, nous allons étudier plus en détail le matériel lié au réseau. Nous allons notamment étudier les hub et switchs, ainsi que les routeurs. Les câbles réseau seront aussi probablement de la partie. Il existe différents protocoles pour gérer la transmission sur un réseau, mais seuls les protocoles Ethernet, MAC et IP sont pertinents pour ce chapitre. Ces protocoles sont séparés entre protocoles de couche liaison et de couche routage. Les premiers se chargent de la communication sur un réseau local, sans passer avec un intermédiaire (réseau local). Par exemple, les protocoles MAC et Ethernet s'occupent de la transmission d'informations entre deux ordinateurs reliés par un câble réseau ou via un réseau local (à travers un concentrateur/commutateur, comme on le verra plus loin). Les protocoles de routage, quant à eux, gèrent les transferts sur des réseaux étendus internet) et la transmission par un grand nombre d'ordinateurs intermédiaires.

Les commutateurs

Il existe plusieurs types de réseaux locaux, mais ceux que nous allons étudier sont des réseaux en étoile, où tous les ordinateurs sont reliés à un équipement central. L'équipement central sert de relai aux trames : il reçoit des trames et les envoie aux ordinateurs de destination. Suivant la manière dont fonctionne l'équipement central, on distingue le concentrateur du commutateur. Un concentrateur redistribue chaque donnée reçue sur tous les autres ports, sans se préoccuper de sa destination : c'est l'équivalent réseau d'un bus. Les concentrateurs sont à contraster avec les commutateurs, au fonctionnement similaire, mais qui n'envoient les données qu'au composant de destination. Avec un concentrateur, les données émises sont envoyées à tous les autres ordinateurs. Pas besoin de parler plus en détail du concentrateur : nous avons déjà parlé des bus dans un chapitre à part et le concentrateur en lui-même n'est rien d'autre qu'un bus ! Par contre, il est intéressant de parler du commutateur.

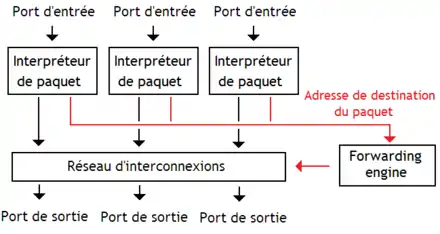

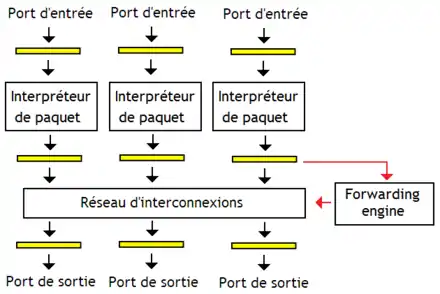

Rappelons que les données sont transmises sur le réseau local sous la forme de trames, des blocs de données de taille fixe. Chaque trame contient à la fois des données utiles, mais aussi un en-tête qui contient toutes les informations nécessaires à la gestion de la trame. Notamment, chaque trame indique d'elle-même sa destination dans le réseau, ce qui permet au commutateur de savoir à quel ordinateur transmettre la trame. L'ordinateur de destination est identifié par une adresse MAC de 6 octets (48 bits). Lorsqu'il reçoit une trame, le commutateur l'analyse, déduit quel est l'ordinateur de destination et renvoie la trame sur le port associé à l'ordinateur de destination. Pour faire ce travail, le commutateur dispose de plusieurs sous-circuits :

- Un circuit extrait l'adresse MAC de destination des trames reçues (l'analyseur de trames).

- Un circuit qui décide, en fonction de l'adresse MAC de destination, sur quel port l'envoyer (le forwarding engine).

- Un circuit d'interconnexion qui relie chaque port à tous les autres.

L'encapsulation et la commutation

Avant de nous intéresser au circuit d'interconnexion, nous allons étudier les deux autres circuits, à savoir : l'interpréteur de paquets, qui détecte ou analyse les trames/paquets, et le Forwarding Engine, qui détermine le port de destination à partir de l'adresse de destination. Rappelons que le switch est un matériel qui gère trames et que chacune d'entre elle indique l'adresse MAC du destinataire et de l'émetteur. À l'intérieur du forwarding engine, on trouve une table de correspondance qui associe chaque adresse MAC à un port : la CAM table. Elle peut être implémentée de deux manières : avec une machine à états finis matérielle ou avec une mémoire RAM ou associative. La dernière solution est la plus utilisée, même si des solutions hybrides sont aussi relativement courantes (on peut notamment citer l'algorithme de routage nommé Logic-Based Distributed Routing).

Un commutateur doit découvrir par lui-même les adresses MAC des composants qu'on branche sur ses ports : il ne peut pas les connaitre à l'avance. Pour cela, le commutateur utilise une méthode assez simple. Imaginons que la table CAM soit vide : le commutateur ne sait pas qui est qui sur ses sports. Si un ordinateur lui envoie une trame sur un port, il met à jour la table CAM avec l'adresse de l'émetteur de la trame : cela fait un port de connu. Une fois que tous les ordinateurs ont envoyé quelque chose sur le réseau, il connait tous les ports. Si aucun port n'est associé à une adresse de destination, le commutateur envoie le paquet à tous les autres ports.

Il faut noter que le contenu de la table CAM a une durée de péremption. Cela permet de mettre à jour un réseau local sans avoir à redémarrer le commutateur : on peut changer le composant branché sur un commutateur, celui-ci ne restera pas bloqué sur l'ancien composant et finira par repérer le nouveau au bout d'un certain temps. Cette durée de péremption est appelée le Time To Live, ou TTL, et vaut entre 0 et 255 secondes.

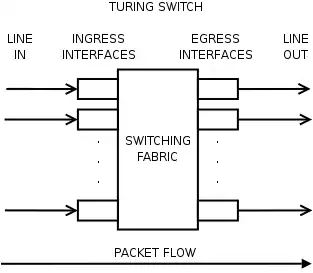

Le circuit d'interconnexion (Switch Fabric)

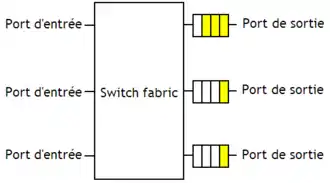

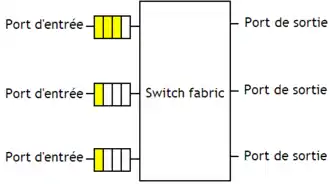

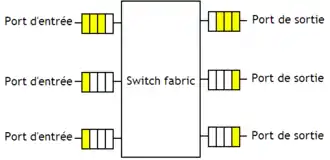

Une fois que le port de destination est connu, le commutateur/routeur en déduit quels ports il faut connecter entre eux. Pour cela, il a juste à configurer un circuit d'interconnexion, qui relie les ports entre eux et qui est équivalent à un ensemble de connexions point à point configurables. Ce circuit d'interconnexion porte un nom : c'est la switch fabric. Il suffit de lui envoyer le numéro du port d'entrée et du port de sortie et le circuit d'interconnexion connecte ces deux ports (les autres ports restent déconnectés, en principe et sauf optimisation).

Les techniques de broadcast ou de multicast permettent d'envoyer une donnée présentée sur un port d'entrée sur plusieurs sorties : on peut envoyer un message identique à plusieurs ordinateurs en même temps, sans devoir envoyer plusieurs copies. Certains switchs permettent de gérer cela directement dans le matériel, soit en dupliquant les paquets, soit en connectant une entrée sur plusieurs sorties. Certains switchs traitent les ports d'entrée à tour de rôle, l'un après l'autre : on parle de switchs à partage de temps, aussi appelés time-sharing switch chez les anglo-saxons. D'autres switchs permettent de gérer tous les ports d'entrée à la fois : on parle de switchs à partage d'espace, ou space-sharing switchs chez les anglo-saxons.

Switchs à partage d'espace

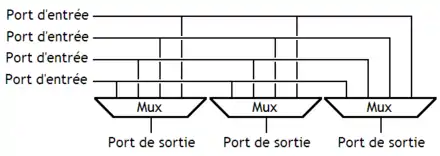

Les switchs à partage d'espace sont de loin les plus simples à comprendre. Ceux-ci sont simplement composés d'un ensemble de liaisons point à point, qui relient chacune un port d'entrée à un port de sortie. Chaque port d'entrée est relié à chaque port de sortie, chaque liaison pouvant être activée ou désactivée selon les besoins.

Il est possible de concevoir ce circuit avec des multiplexeurs.

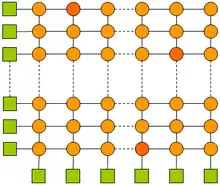

Il est aussi possible d'utiliser un réseau crossbar. Ce dernier est composé de fils organisés en lignes et en colonnes. À l'intersection de chaque ligne et de colonne, on trouve un interrupteur qui relie la ligne et la colonne.

On peut utiliser plusieurs switchs crossbar pour former un switch plus gros, les différentes manières donnant respectivement un réseau CLOS, un réseau de Benes, un réseau de banyan, les Switch Sunshine, et bien d'autres.

Dans ce qui va suivre, nous allons nous intéresser aux switchs de Banyan, des swiths fabrics conçues à partir de switchs à deux entrées et deux sorties. Cependant, on peut adapter les switchs de Banyan pour qu'ils n'utilisent pas des switchs 2 - 2, mais 3 - 3, ou 4 - 4, voire plus : on parle alors de switchs de Banyan augmentés. Qui plus est, ces briques de base peuvent contenir des FIFO et de la logique de traitement, comme pour les switch Crossbar. Ces switchs sont empilés pour former des couches, chaque couche possédant autant de sorties et d'entrée qu'il y en a dans le switch de Banyan final : si un switch a 8 entrées et 8 sorties, alors chaque couche aura 8 sorties et 8 entrées (et cela marche aussi avec 4, 16, etc). Le nombre de couches est égal au logarithme du nombre de ports d'entrée/sortie N, ce qui fait que le nombre de switchs de base utilisé est proportionnel à N × log (N) : on économise donc des portes logiques comparé à un crossbar.

Le switch de Banyan le plus simple est composé de deux couches, et possède donc 4 entrées et 4 sorties. Il ressemble à ceci :

.png.webp)

Pour un switch à 8 entrées et 8 sorties, voici ce que cela donne :

.png.webp)

Et ainsi de suite…

En guise d'exercice, regardez bien les schémas, et essayez d'en déduire la logique de construction. Vous verrez, rien de bien sorcier. Et non, je ne pose pas cet exercice parce que j'ai la flemme de vous l'expliquer... Blague à part, il existe différents types de réseaux de Banyan, qui portent les doux noms d'Omega, d'Alpha, etc. Ces réseaux se construisent simplement : si on prend un switch à N entrées (et autant de sorties), alors chaque couche doit réaliser une permutation des entrées et sorties, permutation qui doit respecter certaines propriétés pour tenir compte du fait que les switchs de base ont deux entrées et deux sorties. Le principe de création dépend donc des permutations utilisées sur chaque couche.

Mais ces switchs ne sont pas sans défauts. En effet, ces switchs sont dits bloquants : il se peut que deux paquets destinés à des ports de destination différents ne puissent pas voir leurs demandes assouvies simultanément. Cela arrive quand deux paquets veulent sortir sur le même port d'un des switch 2 - 2, d'où conflit. Cependant, on peut éviter ces conflits internes en triant les paquets suivant leur port de destination avec un algorithme bien précis. En conséquence, certains switchs de Banyan sont précédés d'un circuit de tri conçu avec des switchs 2 - 2, empilés en couches, ainsi qu'avec de la logique de configuration composée de comparateurs : l'ensemble forme un switch Batcher-Banyan.

Switchs à partage de temps

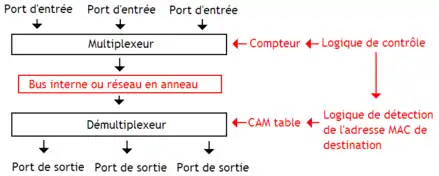

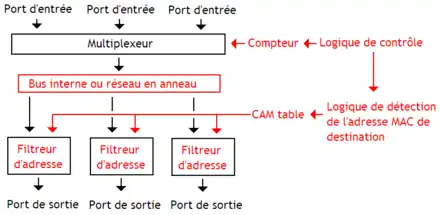

Les switchs à partage de temps émulent les liaisons point à point à partir d'un bus ou d'un réseau en anneaux : ce sont les switchs à média partagés.

Avec cette architecture, implémenter le multicast ou le broadcast est relativement complexe. Pour résoudre ce problème, il suffit de relier chaque port de sortie sur le bus interne directement, sans démultiplexeur. En faisant cela, chaque port de sortie doit filtrer les paquets qui ne lui sont pas destinés. Pour cela, on ajoute un filtre d'adresse pour comparer l'adresse MAC/IP associée au port (CAM table) et l'adresse MAC de destination : s'il y a égalité, alors on peut recopier la donnée sur le port de sortie. Ces switchs sont des switchs à partage de temps (sauf le tout premier).

Arbitrage

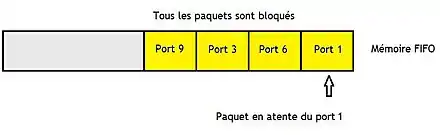

La switch fabric est relativement lente comparée au temps d'envoi et de réception d'un paquet, ce qui fait qu'il est nécessaire de mettre ceux-ci en attente tant que la switch fabric est occupée avec le paquet précédent. De même, il faut gérer le cas où plusieurs paquets veulent accéder au même port de sortie, ce qui impose d'envoyer les paquets les uns après les autres, certains étant mis en attente (il arrive cependant que certains paquets soient perdus). Dans tous les cas, qui dit mise en attente dit : utilisation de mémoires tampons de type FIFO.

Arbitrage hors de la switch fabric

Si les tampons sont remplies, les paquets en trop sont perdus et n'arrivent pas à destination : on laisse la situation entre les « mains » du logiciel.

Certains tampons FIFO sont placés entre la switch fabric et l'interface réseau de sortie, au cas où celle-ci soit plus lente que la switch fabric : on parle d'output buffering.

D'autres sont placés en entrée de la switch fabric, celle-ci pouvant mettre du temps à traiter les paquets qui lui arrivent : on parle d'input buffering.

Il est parfaitement possible d'utiliser les deux en même temps, ce qui porte le nom d'input-output buffering.

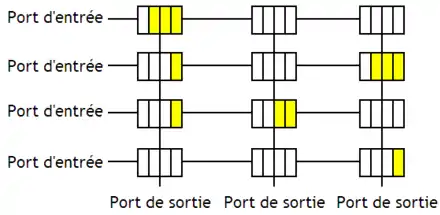

Si une requête est en attente via input buffering, elle va bloquer les requêtes suivantes sur le port d'entrée, même si celles-ci ont un port de sortie différent : on parle d'head of line blocking. Pour l'éliminer, certains switchs utilisent le Virtual output queing, à savoir découper chaque tampon FIFO en sous-tampons, chacun prenant en charge les paquets destinés à un port de sortie précis. Avec cette technique, on peut traiter les requêtes dans le désordre, afin de profiter au maximum des ports libres.

Arbitrage dans la switch fabric

Certains switchs intégrent l'arbitrage directement dans la switch fabric, en intégrant les tampons FIFO dans celle-ci. Dans le cadre d'un switch à partage d'espace, à base de crossbar, l'incorporation de l'arbitrage est relativement aisée. Il suffit de remplacer les interrupteurs ligne/colonne par des tampons FIFO. Le nombre de FIFO est de N * M pour un switch à N ports d'entrée et M ports de sortie. Pour les switchs qui ont un grand nombre de ports d'entrée et de sortie, cela devient rapidement impraticable. Pour éviter cela, les switchs à haute performance réduisent la taille des FIFO intégrées dans le crossbar, mais rajoutent de grosses FIFO sur les ports d'entrée (par ajout d'input buffering). Les simulations montrent que le rapport entre performance et nombre de portes logiques utilisées est meilleur avec cette technique.

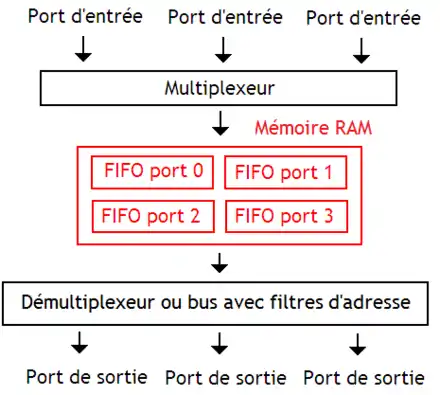

Arbitrage pour les switchs à partage d'espace

Pour les switch à partage d'espace, les tampons FIFO sont incorporés directement entre le MUX pour les ports d'entrée, et le reste (filtreur d'adresse ou DEMUX). Ces FIFOS sont généralement implémenté avec une mémoire RAM. D'où le nom de switchs à mémoire partagée donné à de tels switchs. Ces switchs permettent de gérer l'arbitrage directement dans la switch fabric : la mémoire centrale stocke les données des tampons FIFO d'arbitrage des ports d'entrée. Le switch présenté dans le schéma ci-dessous peut être transformé en switch sans partage de temps avec une mémoire multiport : il suffit d'avoir autant de ports d'écriture que de ports d'entrée, et d'adapter les circuits de gestion de la mémoire. Dans ce qui va suivre, mes schémas utiliseront un switch à partage de temps.

Reste que ces tampons FIFO peuvent s'implémenter de différentes manières. La solution la plus simple consiste à utiliser un cache (une mémoire associative, plus précisément). Chaque ligne de ce cache mémorise un paquet, son numéro de port de sortie et son ordre d'envoi (afin de simuler une FIFO). Pour mémoriser l'ordre d'envoi, le switch attribue un numéro de séquence à chaque paquet : plus ce numéro est grand, plus le paquet est ancien. Obtenir le prochain paquet à envoyer demande simplement d'envoyer le numéro du prochain paquet (déterminé par un compteur) et le numéro du port de sortie à la mémoire associative. Celle-ci renvoie alors le paquet à envoyer sur ce port de sortie.

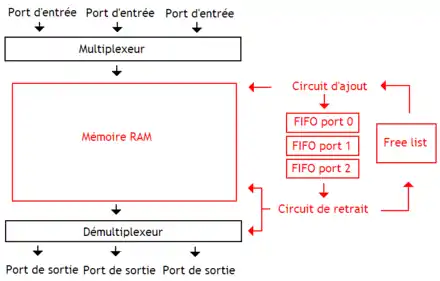

Une autre solution consiste à utiliser une mémoire RAM pour stocker les paquets dans des listes doublement chainées. Il y a une liste par port de sortie : tous les paquets destinés à un port de sortie sont ajoutés à la liste qui lui est associée. Les circuits qui gèrent la mémoire RAM doivent gérer eux-mêmes les listes chaînées, ce qui fait qu'ils contiennent deux registres par liste : un pour l'adresse en tête de liste et un pour le dernier élément. Il y a un circuit pour l'ajout et un autre pour le retrait des paquets. En plus de cela, les circuits de gestion de la mémoire doivent allouer dynamiquement les nœuds de la liste et libérer la mémoire. La mémoire utilise des Bytes démesurément grands, capables de mémoriser un paquet de plusieurs centaines de bits sans problèmes. Ainsi, le switch a juste besoin de mémoriser quels sont les Bytes libres et les Bytes occupés dans une mémoire annexe : la free list, souvent implémentée avec une mémoire FIFO.

- Une première méthode mémorise les données dans la RAM, ainsi que l'ordre de stockage des paquets.

- La deuxième méthode réserve la mémoire centrale pour le stockage des paquets et maintient l'ordre d'envoi des paquets dans des tampons FIFO, qui mémorisent les adresses des paquets dans la mémoire centrale. La taille fixe des mémoires FIFO ne permet pas d'allouer toute la mémoire pour seulement quelques ports. Mais cette organisation permet de gérer facilement le multicast et le broadcast : on peut facilement ajouter un paquet dans toutes les mémoires FIFO, simultanément avec un circuit d'ajout conçu pour.

Les routeurs

Il est maintenant temps de laisser les réseaux locaux derrière nous, et de voir plus grand. Par plus grand, je veux dire que nous allons aborder le réseau Internet. Sur le réseau Internet, les données sont transmises en paquets de taille variable, qui sont appelés sobrement des paquets réseau, ou encore des paquets. Chaque paquet se propage dans le réseau de proche en proche, passant par de nombreux intermédiaires avant d'arriver à destination. Ces intermédiaires sont appelés des routeurs.

Les routeurs sont similaires aux commutateurs, si ce n'est qu'ils gèrent des adresses différentes des adresses MAC : les adresses IP. Ces dernières permettent d'identifier un ordinateur sur Internet, mais n'a pas de lien avec les adresses MAC (qui sont limitées aux réseaux locaux). Pour simplifier, les routeurs reçoivent des paquets sur un port d'entrée, qui sont destinés à une adresse IP de destination, qui doit être envoyé à l'ordinateur de destination. Son fonctionnement est similaire à celui d'un commutateur amélioré. La seule différence notable est que la table CAM est remplacée par une table de routage, qui associe une adresse IP de destination au port de sortie qui correspond.

Routeurs de première génération

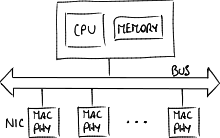

Les tout premiers routeurs, dits de première génération, relient leurs ports d'entrée et de sortie avec un bus. ils contiennent aussi un processeur tout ce qu'il y a de plus normal pour traiter les trames IP, ainsi qu'une mémoire RAM pour stocker les trames et la table de routage. Chaque port est relié à de circuits chargés de gérer le port. Ces circuits reçoivent des trames, les envoient et effectuent quelques traitements basiques. Ils gèrent notamment tout ce qui a trait aux adresses MAC. Une fois que ces circuits ont fait leur office, ils envoient la trame traitée sur le bus interne au routeur. La trame est alors réceptionnée par le processeur, éventuellement stockée en mémoire RAM. Celui-ci accède alors à la table de routage, pour identifier le port de sortie. Enfin, le processeur envoie la trame vers le port de sortie qu'il a déduit de ses traitements. La trame est alors envoyée sur le réseau. Le défaut principal de ce type de routeur est que les transferts en direction du processeur principal saturent le bus dans certaines situations critiques.

Routeurs de seconde génération

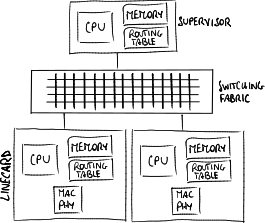

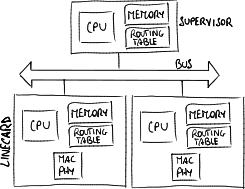

Les routeurs de seconde génération sont plus complexes. Ceux-ci multiplient le processeur, la RAM et la table de routage en plusieurs exemplaires : un exemplaire par port. Ainsi, les trames reçues sur un port sont directement traités dans les circuits de gestion de ce port. Une fois traitée, elles sont envoyées directement sur le port de sortie, et envoyée immédiatement sur le réseau. Cependant, cela ne vaut que pour des trames simples. Les trames plus complexes doivent être traitées par un processeur plus complexe, non-attaché à un port. Ce processeur, le superviseur, est unique dans le routeur.

Routeurs de troisième génération

Cependant, les deux types de routeurs précédents utilisent un bus pour afin de faire communiquer les différents composants. Or, il se peut que les conflits d'accès au bus minent les performances. Pour éviter cela, certains routeurs remplacent le bus par une switch fabric, pour gagner en performance. Ainsi, les transfert n'entrent pas en conflit pour l'accès à un unique bus, chaque transfert pouvant se faire en parallèle des autres.