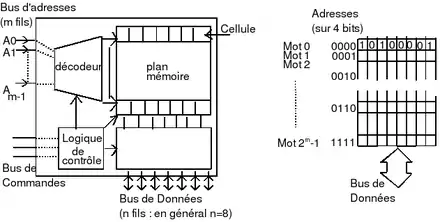

La gestion de l'adressage et de la communication avec le bus sont assurées par un circuit spécialisé : le contrôleur mémoire. Une mémoire adressable est ainsi composée :

- d'un plan mémoire ;

- du contrôleur mémoire, composé d'un décodeur et de circuits de contrôle ;

- et des connexions avec le bus.

Nous avons vu le fonctionnement du plan mémoire dans les chapitres précédents. Les circuits qui font l'interface entre le bus et la mémoire ne sont pas différents des circuits qui relient n'importe quel composant électronique à un bus, aussi ceux-ci seront vus dans le chapitre sur les bus. Bref, il est maintenant temps de voir comment fonctionne un contrôleur mémoire. Je parlerai du fonctionnement des mémoires multiports dans le chapitre suivant.

Les mémoires à adressage linéaire

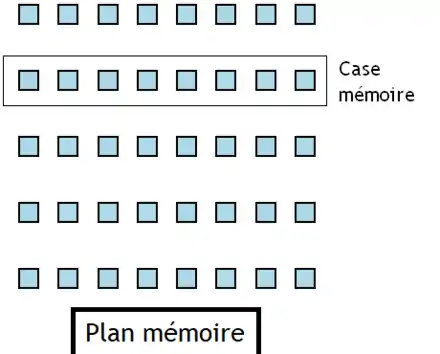

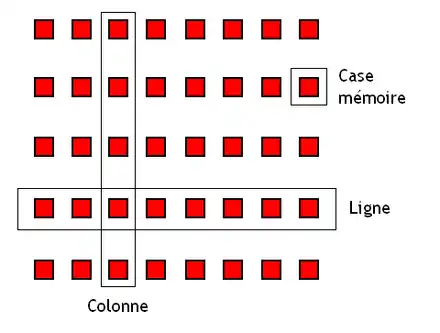

Pour commencer, nous allons voir les mémoires à adressage linéaire. Sur ces mémoires, le plan mémoire est un tableau rectangulaire de cellules mémoires, et toutes les cellules mémoires d'une ligne appartiennent à une même case mémoire. Les cellules mémoire d'une même colonne sont connectées à la même bitline. Avec cette organisation, la cellule mémoire stockant le énième bit du contenu d'une case mémoire (le bit de poids i) est reliée au énième fil du bus. Rappelons que chaque ligne est reliée à un signal de sélection de ligne Row Line, qui permet de connecter les cellules mémoires du byte adressé à la bitline.

Le rôle du contrôleur mémoire est de déduire quelle entrée Row Line mettre à un à partir de l'adresse envoyée sur le bus d'adresse. Pour cela, le contrôleur mémoire doit répondre à plusieurs contraintes :

- il reçoit des adresses codées sur n bits : ce contrôleur a donc n entrées ;

- l'adresse de n bits peut adresser 2n bytes : notre contrôleur mémoire doit donc posséder 2^n sorties ;

- la sortie numéro N est reliée au N-iéme signal Row Line (et donc à la N-iéme case mémoire) ;

- on ne doit sélectionner qu'une seule case mémoire à la fois : une seule sortie devra être placée à 1 ;

- et enfin, deux adresses différentes devront sélectionner des cases mémoires différentes : la sortie de notre contrôleur qui sera mise à 1 sera différente pour deux adresses différentes placées sur son entrée.

Le seul composant électronique qui répond à ce cahier des charges est le décodeur, ce qui fait que le contrôleur mémoire se résume à un simple décodeur, avec quelques circuits pour gérer le sens de transfert (lecture ou écriture), et la détection/correction d'erreur. Ce genre d'organisation s'appelle l'adressage linéaire.

Les mémoires à adressage par coïncidence

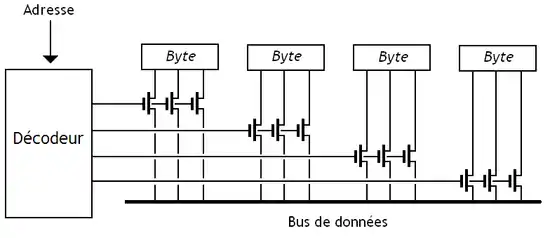

Sur des mémoires ayant une grande capacité, le décodeur utilise trop de portes logiques et le temps de propagation augmente à cause du nombre de lignes. Pour éviter cela, certaines mémoires regroupent plusieurs cases mémoires sur une seule ligne, ce qui, pour un nombre de cases mémoires fixé, diminue le nombre de lignes.

Adresser la mémoire demande alors de sélectionner la ligne voulue, et de sélectionner la case mémoire à l'intérieur de la ligne. Sélectionner une ligne est facile : on utilise un décodeur. Mais la méthode utilisée pour sélectionner la colonne dépend de la mémoire utilisée. Commençons par aborder la première méthode, celle des mémoires à adressage par coïncidence.

L'adressage par coïncidence

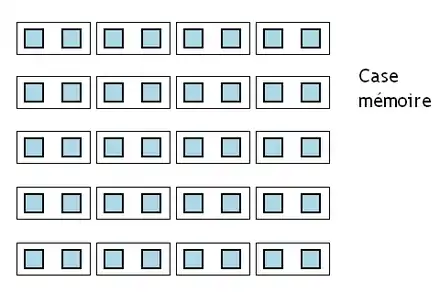

Sur ces mémoires, les cases mémoires sont organisées en lignes et en colonnes, avec une case mémoire à l'intersection entre une colonne et une ligne.

Toutes les cases mémoires d'une colonne sont reliées à un autre fil, le column line. Une case mémoire est sélectionnée quand ces row lines et la column line sont tous les deux mis à 1 : il suffit d'envoyer ces deux signaux aux entrées d'une porte ET pour obtenir le signal d'autorisation de lecture/écriture pour une cellule.

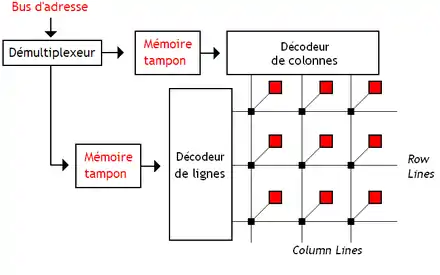

On utilise donc deux décodeurs : un pour sélectionner la ligne (pour le row line) et un autre pour sélectionner la colonne. Sur certaines mémoires, les deux décodeurs fonctionnent en même temps : on peut décoder une ligne en même temps qu'une colonne. Sur d'autres, on envoie les adresses en deux fois : d'abord l'adresse de ligne, puis l'adresse de colonne. Cela permet d'économiser des fils sur le bus d'adresse, mais nécessite de mémoriser les deux morceaux de l'adresse : si la mémoire ne se souvient pas de l'adresse de la ligne, elle ne pourra pas sélectionner le byte voulu. Pour cela, on place deux registres, entre les décodeurs et le bus d'adresse. Il faut aussi ajouter de quoi aiguiller le contenu du bus d'adresse vers le bon registre, en utilisant un démultiplexeur.

Les mémoires par blocs

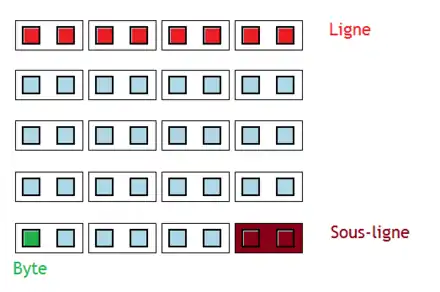

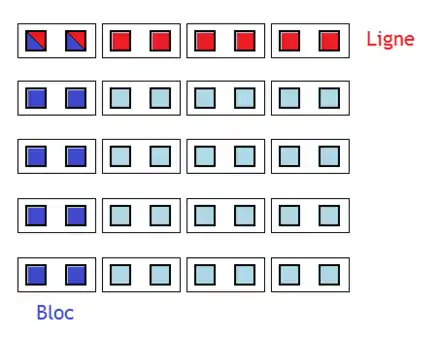

Cette organisation par coïncidence peut être améliorée en rajoutant un troisième niveau de subdivision : chaque ligne est découpée en sous-lignes, qui contiennent plusieurs colonnes. On obtient alors des mémoires par blocs, ou divided word line structures. Chaque ligne est donc découpée en N lignes, numérotées de 0 à N-1. Les sous-lignes qui ont le même numéro sont en quelque sorte alignées verticalement, et sont reliées aux mêmes bitlines : celles-ci forment ce qu'on appelle un bloc. Chacun de ces blocs contient un plan mémoire, un multiplexeur, et éventuellement des amplificateurs de lecture et des circuits d'écriture.

Tous les blocs de la mémoire sont reliés au décodeur d'adresse de ligne. Mais malgré tout, on ne peut pas accéder à plusieurs blocs à la fois : seul un bloc est actif lors d'une lecture ou d'une écriture. Pour cela, un circuit de sélection du bloc se charge d'activer ou de désactiver les blocs inutilisés lors d'une lecture ou écriture. L'adresse d'une sous-ligne bien précise se fait par coïncidence entre une ligne, et un bloc.

La ligne complète est activée par un signal wordline, généré par un décodeur de ligne. Les blocs sont activés individuellement par un signal nommé blocline, produit par un décodeur de bloc : ce décodeur prend en entrée l'adresse de bloc, et génère le signal blocline pour chaque bloc. Ensuite, une fois la sous-ligne activée, il faut encore sélectionner la colonne à l'intérieur de la sous-ligne sélectionnée, ce qui demande un troisième décodeur. L'adresse mémoire est évidemment coupée en trois : une adresse de ligne, une adresse de sous-ligne, et une adresse de colonne.

Les mémoires à row buffer

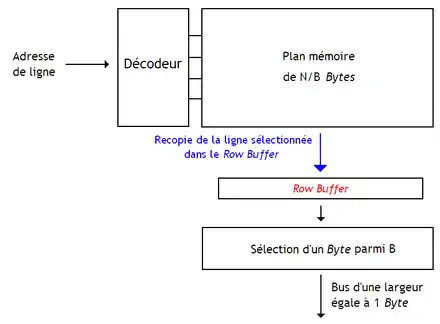

Enfin, nous allons voir une espèce de mélange entre les deux types de mémoires vus précédemment : les mémoires à row buffer. Une mémoire à row buffer émule une mémoire de N bytes à partir d'une mémoire contenant B fois moins de bytes, mais dont chacun des bytes seront B fois plus gros. Chaque accès va lire un « super-byte » de la mémoire interne, et sélectionner le bon byte dans celui-ci. Sur le schéma du dessous, on voit bien que notre mémoire est composée de deux grands morceaux : une mémoire à adressage linéaire, et un circuit de sélection d'un mot mémoire parmi B (souvent un multiplexeur).

Sur la grosse majorité de ces mémoires, chaque ligne sélectionnée est recopiée intégralement dans un registre temporaire, le row buffer, dans lequel on viendra sélectionner la case mémoire correspondant à notre colonne.

Les plans mémoire à row buffer récupèrent les avantages des plans mémoires par coïncidence : possibilité de décoder une ligne en même temps qu'une colonne, possibilité d'envoyer l'adresse en deux fois, consommation moindre de portes logiques, etc. De plus, cela permet d'effectuer l'opération de rafraichissement très simplement, en rafraichissant une ligne à la fois, au lieu d'une case mémoire à la fois. Autre avantage : en concevant correctement la mémoire, il est possible d'améliorer les performances lors de l'accès à des données proches en mémoire : si on doit lire ou écrire deux mots mémoires localisés dans la même ligne de notre mémoire interne, il suffit de charger celle-ci une fois dans le row buffer, et de faire deux sélections de colonnes différentes. C'est plus rapide que de devoir faire deux sélections de lignes et deux de colonnes. On en reparlera lorsqu'on verra les mémoires SDRAM et EDO.

Par contre, cette organisation consomme beaucoup d'énergie. Il faut dire que pour chaque lecture d'un byte dans notre mémoire, on doit charger une ligne de plusieurs cases mémoires dans le row buffer.