De nos jours, ces cellules mémoires sont fabriquées avec des composants électroniques et il nous faudra impérativement passer par une petite étude de ces composants pour comprendre comment fonctionnent nos mémoires. Dans les grandes lignes, les mémoires RAM et ROM actuelles sont toutes composées de cellules mémoires, des circuits capables de retenir un bit. En prenant plein de ces cellules et en ajoutant quelques circuits électroniques pour gérer le tout, on obtient une mémoire. Dans ce chapitre, nous allons apprendre à créer nos propres bits de mémoire à partir de composants élémentaires : des transistors et des condensateurs.

L'interface d'une cellule mémoire (généralités)

Les cellules mémoires se présentent avec une interface simple, limitée à quelques broches. Et cette interface varie grandement selon la mémoire : elle n'est pas la même selon qu'on parle d'une DRAM ou d'une SRAM, avec quelques variantes selon les sous-types de DRAM et de SRAM. Là où les DRAM se limitent souvent à deux broches, les SRAM peuvent aller jusqu'à quatre. Nous reparlerons dans la suite des interfaces pour chaque type (voire sous-type) de mémoire. Pour le moment, nous allons commencer par voir le cas général. Dans les grandes lignes, on peut grouper les broches d'une cellule mémoire en plusieurs types :

- Les broches de données, sur lesquelles on va lire ou écrire un bit.

- Les broches de commande, sur lesquelles on envoie des ordres de lecture/écriture.

- D'autres broches, comme la broche pour le signal d'horloge ou les broches pour l’alimentation électrique et la masse.

Les broches de données

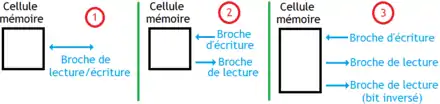

Concernant les broches de données, il y a plusieurs possibilités qui comprennent une, deux ou trois broches.

- Dans le cas le plus simple, on peut interagir avec une cellule mémoire via deux broches. La première est une broche d'entrée-sortie, sur laquelle on peut écrire ou lire un bit.

- Les cellules mémoires plus compliquées scindent cette broche d'entrée/sortie en deux : une broche de lecture, sur laquelle on peut lire le bit stocké dans la cellule, et une broche d'écriture, sur laquelle on place le bit à stocker dans la cellule.

- Sur certaines cellules mémoire, on ajoute une broche qui fournit l'inverse du bit stocké. Nous en avons déjà vu un exemple quand nous avons parlé des bascules, dans le chapitre sur les circuits séquentiels.

Les broches de commande

Pour les broches de commande, il y a deux possibilités : soit la cellule reçoit un bit Enable couplé à un bit R/W, soit elle possède deux bits qui autorisent respectivement les lectures et écriture.

- La forme la plus simple est une broche de sélection qui autorise/interdit les communications avec la cellule mémoire. Cette broche de sélection connecte ou déconnecte les autres broches du reste de la mémoire. Elle est couplée, dans le cas des mémoires RAM, à une broche R/W, sur laquelle on vient placer le fameux bit R/W, qui dit s'il faut faire une lecture ou une écriture.

- Encore une fois, elle peut être scindée en une broche d'autorisation de lecture et une broche d'autorisation d'écriture, sur laquelle on place le bit R/W (ou son inverse) pour autoriser/interdire les écritures.

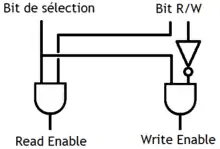

Conversions entre interfaces de commande

Il est possible de passer d'une interface à l'autre assez simplement, grâce à un petit circuit à ajouter à la cellule mémoire. Cela est utile pour faciliter la conception du contrôleur mémoire. Celui-ci peut en effet générer assez simplement le signa Enable, à envoyer sur la broche de sélection. Quant au bit R/W, il est fournit directement à la mémoire, via le bus de commande. L'interface avec les broches Enable et R/W est donc la plus facile à utiliser. Mais si on regarde l'intérieur de certaines cellules mémoire (celles de SRAM, notamment), on s’aperçoit que leur organisation interne se marie très bien avec la seconde interface, celle avec une broche d'autorisation de lecture et une pour autoriser les écritures. Il faut donc faire la conversion de la seconde interface vers la première.

Pour cela, on ajoute un petit circuit qui convertit les bits Enable et R/W en signaux d'autorisation de lecture/écriture. On peut établir la table de vérité de ce circuit assez simplement. Déjà, les deux bits d'autorisation ne sont à 1 que si le signal de sélection est à 1 : s'il est à 0, la cellule mémoire doit être totalement déconnectée du bus. Ensuite, la valeur de ces deux bits sont l'inverse l'une de l'autre : soit on fait une lecture, soit on fait une écriture, mais pas les deux en même temps. Pour finir, on peut utiliser la valeur de R/W pour savoir lequel des deux bit est à mettre à 1. On a donc le circuit suivant.

Les cellules de SRAM

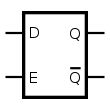

Les cellules de SRAM ont bien évoluées depuis les toutes premières versions jusqu’au SRAM actuelles. Les toutes premières versions ne sont rien de plus que les bascules D vues dans le chapitre sur les circuits séquentiels. Elles étaient fabriquées à partir de portes logiques, ce qui donne un circuit composé de 10 à 20 transistors. Mais certaines SRAM arrivent à se débrouiller avec un nombre de transistors qui se compte sur les doigts d'une main. Les variantes les plus légères se contentent de 4 transistors, les intermédiaires de 5, et les plus grosses de 6 transistors. En général, moins la cellule contient de transistors, moins elle prend de place et plus elle est avantagée dans la construction de RAM de grande capacité.

L'interface d'une cellule de SRAM

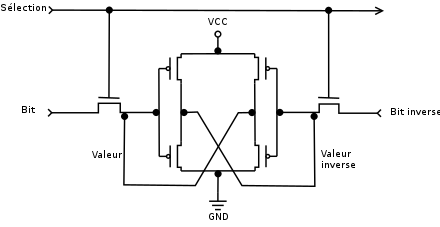

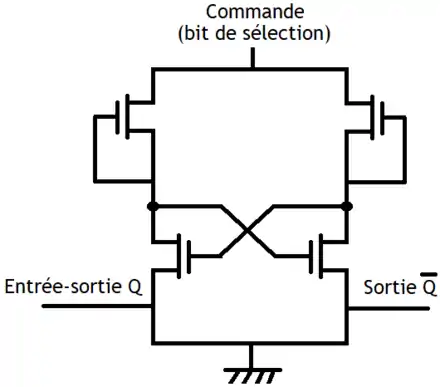

Les cellules de SRAM ont la même interface que les bascules D, à quelques petites différences près. On y trouve, pour simplifier, trois broches, dont deux pour les données et une pour la commande de la bascule. La commande de la bascule est prise en charge par l'entrée Enable, similaire à celle des bascules D. Sur une bascule D, l'entrée Enable ne sert qu'à autoriser les écritures. Mais les choses sont plus compliquées sur les cellules de SRAM. En effet, l'entrée Enable est reliée aux deux transistors de sélection, qui autorisent à la fois les lectures et écritures. L'entrée Enable ne fait donc pas qu'autoriser les écritures, mais aussi les lectures.

Au niveau des données, on trouve deux broches nommées Q et . Le contenu de l'une est l'exact inverse de l'autre : si on trouve un 1 sur l'une, l'autre sera à 0. C'est donc la même chose que sur une bascule D, à un détail près : la broche Q sert ici à la fois pour les lectures et écritures. Sur les bascules D, on trouve une entrée D pour le bit à écrire et une ou deux sorties Q et pour les lectures. Sur une SRAM, rien de tout cela : la sortie Q et l'entrée D sont fusionnées en une seule broche, qui sert à la fois comme entrée d'écriture et comme sortie de lecture.

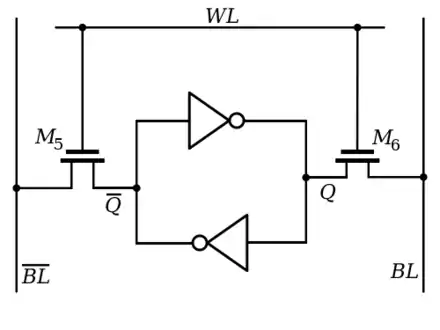

L'intérieur d'une cellule de SRAM

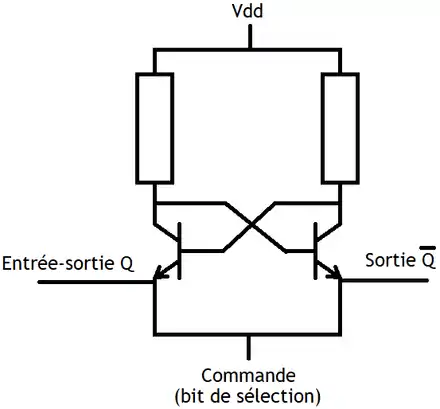

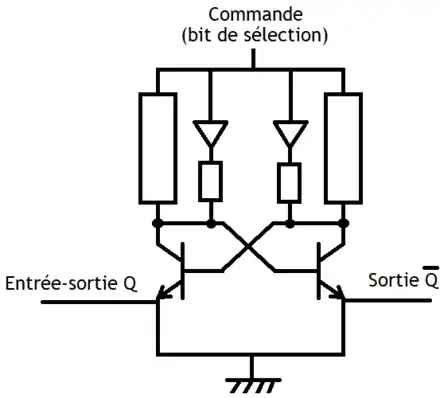

Une bascule de SRAM est construite autour de deux inverseurs reliés tête-bêche (la sortie de l'un sur l'entrée de l'autre), auxquels on ajoute deux transistors qui servent à autoriser les lectures et écritures. Les portes NON reliées tête-bêche mémorisent un bit. Si on place un bit en entrée d'une porte, ce bit sera inversé deux fois avant de retomber sur l'entrée. L'ensemble sera stable : on peut déconnecter l'entrée d'un inverseur, elle sera rafraichie en permanence par l'autre, avec sa valeur précédente. Les deux transistors permettent de connecter les entrées des portes NON sur le bus, afin de modifier ou lire le contenu de la bascule.

Il existe plusieurs types de SRAM, qui se distinguent par la technologie utilisée : bipolaire, CMOS, PMOS, NMOS, etc. Chaque type a ses avantages et inconvénients : certaines fonctionnent plus vite, d'autres prennent moins de place, d'autres consomment moins de courant, etc. La différence tient dans la manière dont ont conçus les portes NON dans la cellule.

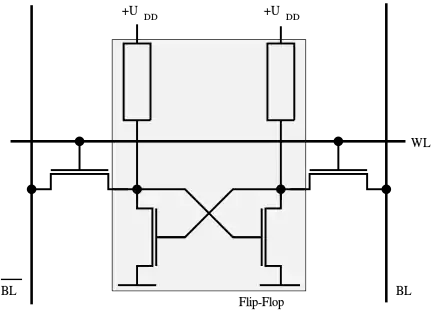

La cellule en technologie CMOS

Les deux inverseurs peuvent être conçus en utilisant la technologie CMOS, bipolaire, NMOS ou PMOS. Dans le cas de la technologie CMOS, chaque inverseur est réalisé avec deux transistors, un PMOS et un NMOS, comme nous l'avons vu dans le chapitre sur les portes logiques. La cellule mémoire obtenue est alors une cellule à 6 transistor : 2 pour l'autorisation des lectures et écritures et 4 pour la cellule de mémorisation proprement dite (les inverseurs tête-bêche). Ce pontage a divers avantages, le principal étant sa très faible consommation électrique. Mais son grand nombre de transistors fait que chaque cellule prend beaucoup de place. On ne peut donc pas l'utiliser pour construire des mémoires de grande capacité.

La cellule en technologie MOS, NMOS ou PMOS

En technologie MOS, ainsi qu'en technologie PMOS et NMOS, chaque porte logique est créée avec un transistor et une résistance. La cellule contient alors, au total, quatre transistors et deux résistances. Le circuit obtenu avec la technologie MOS est illustré ci-dessous.

Il est possible de remplacer la résistance par un transistor MOS câblé d'une manière précise, avec un montage dit en résistance variable. Ce montage fait que le transistor MOS se comporte comme une source de courant, équivalente au courant qui traverse la résistance.

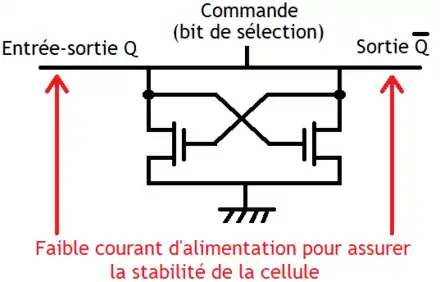

D'autres cellules retirent les résistances de charge, histoire de gagner un peu de place. La réduction de taille de la cellule mémoire est assez intéressante, mais se fait au prix d'une plus grande complexité de la cellule. L'alimentation VDD doit être fournie à l'extérieur de la cellule mémoire, qui doit être alimentée à travers les transistors d'accès. Ceux-ci sont ouverts en-dehors des lectures et écritures, une tension devant être fournie sur leur source/drain, par l'extérieur de la cellule.

La cellule en technologie bipolaire

Les cellules de SRAM en version bipolaire sont de loin les plus rapides, mais leur consommation électrique est bien plus élevée. C'est pour cette raison que les RAM actuelles sont toutes réalisées avec une technologie MOS ou CMOS. Presque aucune mémoire n'est réalisée en technologie bipolaire à l'heure actuelle.

Dans le cas le plus simple, qui utilise le moins de composants, la commande du transistor a lieu au niveau des émetteurs des transistors, qui sont reliés ensemble.

Il est possible d'améliorer le montage en ajoutant deux diodes, une en parallèle de chaque résistance. Cela permet d'augmenter le courant dispensé par la cellule mémoire lors d'une lecture ou écriture. Cela a son utilité, comme on le verra dans le prochain chapitre (pour anticiper : cela rend plus rapide la charge/décharge de la ligne de bit, sans système de précharge). Mais cela demande d'inverser les connexions dans la cellule mémoire. Le circuit obtenu est le suivant.

Les cellules de DRAM

Comme pour les SRAM, les DRAM sont composées d'un circuit qui mémorise un bit, entouré par des transistors pour autoriser les lectures et écritures. La différence avec les SRAM tient dans le circuit utilisé pour mémoriser un bit. Contrairement aux mémoires SRAM, les mémoires DRAM ne sont pas fabriquées avec des portes logiques. A la place, elles utilisent un composant électronique qui sert de "réservoir" à électrons. Un réservoir remplit code un 1, alors qu'un réservoir vide code un 0. La nature du réservoir dépend cependant de la version de la cellule de mémoire DRAM utilisée. Car oui, il existe plusieurs types de cellules de DRAM, qui utilisent des composants réservoir différents. Étudier les versions plus récentes, actuellement utilisées dans les mémoires DRAM modernes, est bien plus facile que de comprendre les versions plus anciennes. Aussi, nous allons commencer par le cas le plus simple : les cellules de DRAM dites 1T-DRAM. Nous verrons ensuite les cellules de type 3T-DRAM, plus complexes et plus anciennes.

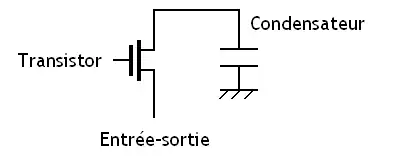

1T-DRAM

Les DRAM actuelles n'utilisent qu'un seul transistor, associé à un autre composant électronique nommé condensateur. Ce condensateur est un réservoir à électrons : on peut le remplir d’électrons ou le vider en mettant une tension sur ses entrées. Il stocke un 1 s'il est rempli, un 0 s'il est vide. C'est donc lui qui sert de circuit de mémorisation. On peut naturellement remplir ou vider un condensateur (on dit qu'on le charge ou qu'on le décharge), ce qui permet d'écrire un bit à l'intérieur.

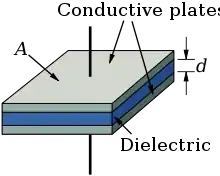

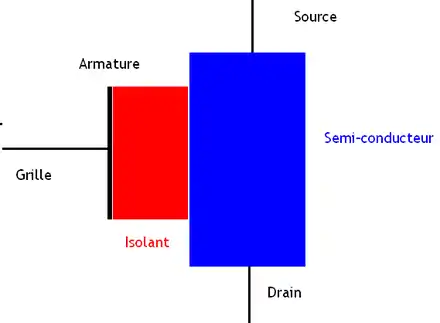

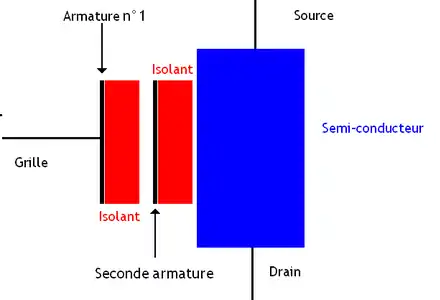

L'intérieur d'un condensateur n'est pas très compliqué : il est formé de deux couches de métal conducteur, séparées par un isolant électrique. Les deux plaques de conducteur sont appelées les armatures du condensateur. C'est sur celles-ci que les charges électriques s'accumulent lors de la charge/décharge d'un condensateur. L'isolant empêche la fuite des charges d'une armature à l'autre, ce qui permet au condensateur de fonctionner comme un réservoir, et non comme un simple fil. Mais sur les DRAM actuelles, les condensateurs sont tellement miniaturisés qu'ils en deviennent de vraies passoires. Il possède toujours quelques défauts et des imperfections qui font que l'isolant n'est jamais totalement étanche : des électrons passent de temps en temps d'une armature à l'autre et quittent le condensateur. En clair, le bit contenu dans la cellule de mémoire DRAM s'efface. Ce qui explique qu'on doive rafraichir régulièrement les mémoires DRAM de ce type.

Autre problème : quand on veut lire ou écrire dans notre cellule mémoire, le condensateur va être connecté sur le bus de données et se vider entièrement : on prend son contenu et il faut le récrire après chaque lecture. Pire : le condensateur se vide sur le bus, mais cela ne suffit pas à créer une tension de plus de quelques millivolts dans celui-ci. Pas de quoi envoyer un 1 sur le bus ! Mais il y a une solution : amplifier la tension de quelques millivolts induite par la vidange du condensateur sur le bus, avec un circuit adapté.

A côté du condensateur, on ajoute un transistor qui va autoriser l'écriture ou la lecture dans notre condensateur. Tant que notre transistor se comporte comme un interrupteur ouvert, le condensateur est isolé du reste du circuit : pas d'écriture ou de lecture possible. Si on l'ouvre, on pourra alors lire ou écrire dedans. Une DRAM peut stocker plus de bits pour la même surface qu'une SRAM : un transistor couplé à un condensateur prend moins de place que 6 transistors.

3T-DRAM

Les premières mémoires DRAM fabriquées commercialement n'utilisaient pas un condensateur, mais un transistor, comme réservoir à électrons. Ils utilisaient le fait qu'il existe, dans tout transistor MOS, un condensateur caché entre la grille et la liaison source-drain. Pour comprendre ce qui se passe dans ce transistor de mémorisation, il savoir ce qu'il y a dans un transistor CMOS. À l'intérieur, on trouve une plaque en métal appelée l'armature, un bout de semi-conducteur entre la source et le drain, et un morceau d'isolant entre les deux. L'ensemble forme donc un condensateur, certes imparfait, qui porte le nom de capacité parasite du transistor. Suivant la tension qu'on envoie sur la grille, l'armature va se remplir d’électrons ou se vider, ce qui permet de stocker un bit : une grille pleine compte pour un 1, une grille vide compte pour un 0.

Cette armature n'est pas parfaite et elle se vide régulièrement, d'où le fait que la mémoire obtenue soit une DRAM. Comme avec les autres DRAM, le bit stocké dans la capacité parasite doit être rafraichit régulièrement. Avec cette organisation, lire un bit ne le détruit pas : on peut relire plusieurs fois un bit sans que celui-ci ne soit effacé. C'est une qualité que les DRAM modernes n'ont pas.

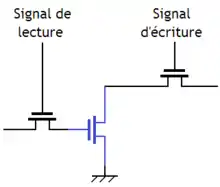

Les DRAM de ce type utilisaient 3 transistors, d'où leur nom de 3T-DRAM. Le bit est mémorisé dans celui du milieu, indiqué en bleu sur le schéma suivant, les deux autres transistors servant pour les lectures et écritures.

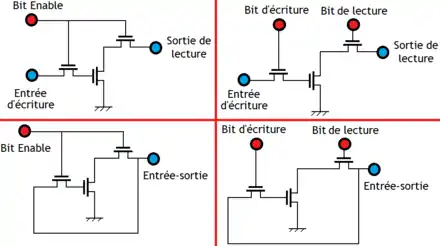

Cette organisation donne donc, dans le cas le plus simple, une cellule avec quatre broches : deux broches de commandes, une pour la lecture et une pour l'écriture, ainsi qu'une entrée d'écriture et une sortie de lecture. Mais il est possible de fusionner certaines broches à une seule. Par exemple, on peut fusionner la broche de lecture avec celle d'écriture. De toute façon, les broches de commande diront si c'est une lecture ou une écriture qui doit être faite. De même, il est possible de fusionner les signaux de lecture et d'écriture, afin de faciliter le rafraichissement de la mémoire. Avec une telle cellule, et en utilisant un contrôleur mémoire spécialement conçu, toute lecture réécrit automatiquement la cellule avec son contenu. Pour résumer, quatre cellules différentes sont possibles, selon qu'on fusionne ou non les broches de données et/ou les broches de commande. Ces quatre possibilités sont illustrées ci-dessous.

Les cellules de mémoires EPROM et EEPROM

Dans le chapitre sur les généralités des mémoires, nous avons vu les différents types de ROM : ROM proprement dite (mask ROM), PROM, EPROM, EEPROM, et mémoire Flash. Ces différents types ne fonctionnent évidement pas de la même manière, non seulement au niveau du contrôleur mémoire, mais aussi des cellules mémoires. Les cellules mémoires des mask ROM et PROM sont un peu à part, dans le sens où elles n'ont pas vraiment de cellule mémoire proprement dit. C'est ce qui fait que le fonctionnement des mémoires PROM et ROM seront vues plus tard, dans un chapitre dédié. Dans ce qui va suivre, nous n'allons voir que les mémoires de type EPROM et leurs dérivés (EEPROM, Flash). Toutes fonctionnent avec le même type de cellule mémoire, les différences étant assez mineures.

Les cellules des EPROM et EEPROM

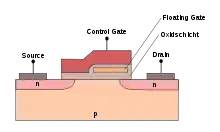

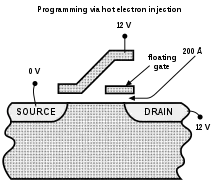

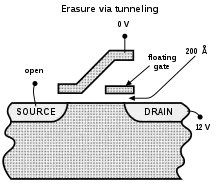

Les mémoires EPROM et EEPROM sont fabriquées avec des transistors à grille flottante (un par cellule mémoire), des transistors qui possèdent deux armatures et deux couches d'isolant. La seconde armature est celle qui stocke un bit : il suffit de la remplir d’électrons pour stocker un 1, et la vider pour stocker un 0. Pour effacer une EPROM, on doit soumettre la mémoire à des ultra-violets : ceux-ci vont donner suffisamment d'énergie aux électrons coincés dans l'armature pour qu'ils puissent s'échapper. Pour les EEPROM, ce remplissage ou vidage se fait en faisant passer des électrons entre la grille et le drain, et en plaçant une tension sur la grille : les électrons passeront alors dans l'armature à travers l'isolant.

Sur la plupart des EEPROM, un transistor à grille flottante sert à mémoriser un bit. La tension contenue dans la seconde armature est alors divisée en deux intervalles : un pour le zéro, et un autre pour le un. De telles mémoires sont appelées des mémoires SLC (Single Level Cell). Mais d'autres EEPROM utilisent plus de deux intervalles, ce qui permet de stocker plusieurs bits par transistor. De telles mémoires sont appelées des mémoires MLC (Multi Level Cell). Évidemment, utiliser un transistor pour stocker deux à trois fois plus de bits aide beaucoup les mémoires MLC à obtenir une grande capacité.

La lecture et l'écriture des cellules des mémoires EEPROM

Les mémoires EEPROM/FLASH sont elles aussi basées sur des transistors à grille flottante, comme les EPROM. La différence tient dans le processus utilisé pour effacer et reprogrammer une cellule. Sur les EEPROM, la reprogrammation et l'effacement de ces cellules demande de placer les bonnes tensions sur la grille, le drain et la source. Le procédé exact est en soit très simple, mais comprendre ce qui se passe exactement est une autre paire de manches. Les phénomènes qui se produisent dans le transistor à grille flottante lors d'une écriture ou d'un effacement sont très compliqués et font intervenir de sombres histoires de mécanique quantique. C’est la raison pour laquelle nous ne pouvons pas vraiment en dire plus.

Mise à 1 de la cellule mémoire (reprogrammation). |

Mise à zéro de la cellule mémoire (effacement). |